#### INTEGRATED CIRCUIT APPLICATIONS

#### **LECTURE NOTES**

B.TECH (III YEAR – I SEM) (2018-19)

Prepared by: Mr. K Murali Krishna, Associate Professor

**Department of Electronics and Communication Engineering**

# MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous Institution – UGC, Govt. of India)

Recognized under 2(f) and 12 (B) of UGC ACT 1956

(Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – 'A' Grade - ISO 9001:2015 Certified)

Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India

#### Unit I

Operational Amplifier

#### Operational Amplifier

- An operational amplifier is a direct coupled high gain amplifier usually consisting of one or more differential amplifier and usually followed by a level translator and an output stage.

- An operational amplifier is available as a single integrated circuit package.

- The operational amplifier is versatile device that can be used to amplify DC as well as AC input signals and was originally designed for computing such mathematical functions as addition, subtraction, multiplication and integration.

### Operational Amplifier cntd...

With the addition of suitable external feedback components, the modern day opamp can be used for a variety of applications such as AC and DC signal amplification, active filters, oscillator, comparators and regulators, and others

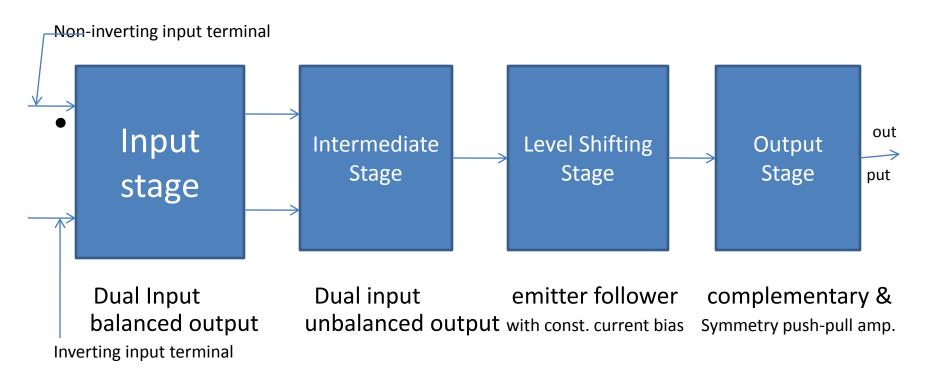

#### Block Diagram of Op-Amp

Since an op-amp is a multi stage amplifier it can be represented by a block diagram as shown in the following figure.

### Block Diagram of Op-Amp cntd...

- The input stage generally provides most of the voltage gain of the amplifier and also establishes the input resistance of the op-amp

- Because of the direct coupling used, the DC voltage at the output of the intermediate stage is well above the ground potential. Therefore, generally, the level translator circuit is used after the intermediate stage

- The final stage is usually a push-pull complimentary amplifier output stage. The output stage increases the output voltage swing and raises the current supplying capability of op-amp. A well designed output stage also provides low output resistance.

#### The IDEAL Op-amp

- An IDEAL op-amp would exhibit the following electrical characteristics.

- Infinite voltage gain, A

- Infinite input resistance Ri

- Zero output resistance Ro

- Zero output voltage when input voltage is zero.

- Infinite bandwidth any signal can be amplified without attenuation

- Infinite common mode rejection ratio

- Infinite slew rate so that output voltage changes occur simultaneously with input voltage changes.

#### Practical Op-amp

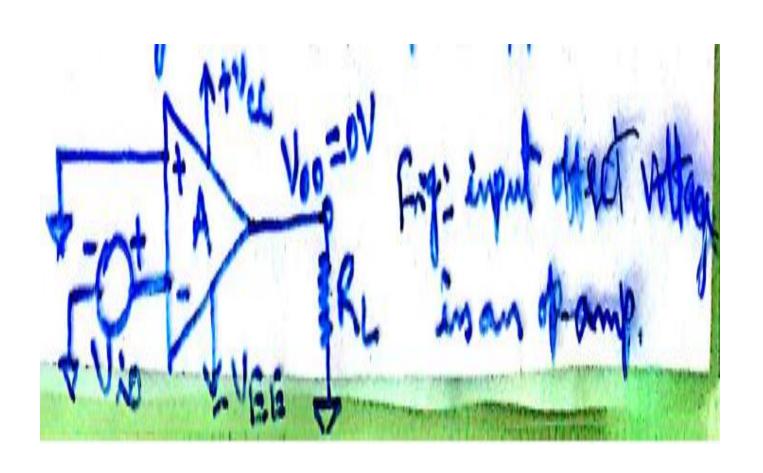

Input offset voltage: Input offset voltage Vio is the differential input voltage that exists between two input terminals of an op-amp with out any external inputs applied.

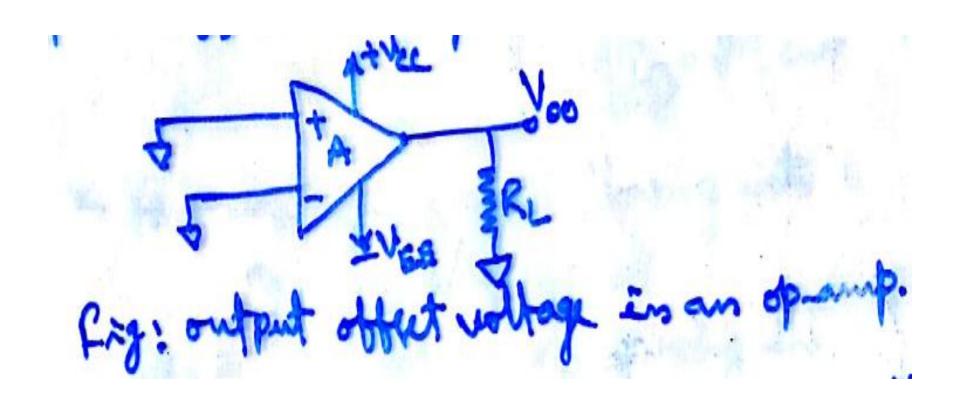

#### Output Offset Voltage:

- The output voltage caused by mismatching between two input terminals is called the output offset voltage Voo.

- The output offset voltage Voo is a DC voltage, it may be +ve or -ve in polarity depending on whether the potential differences between the two input terminals is +ve or -ve.

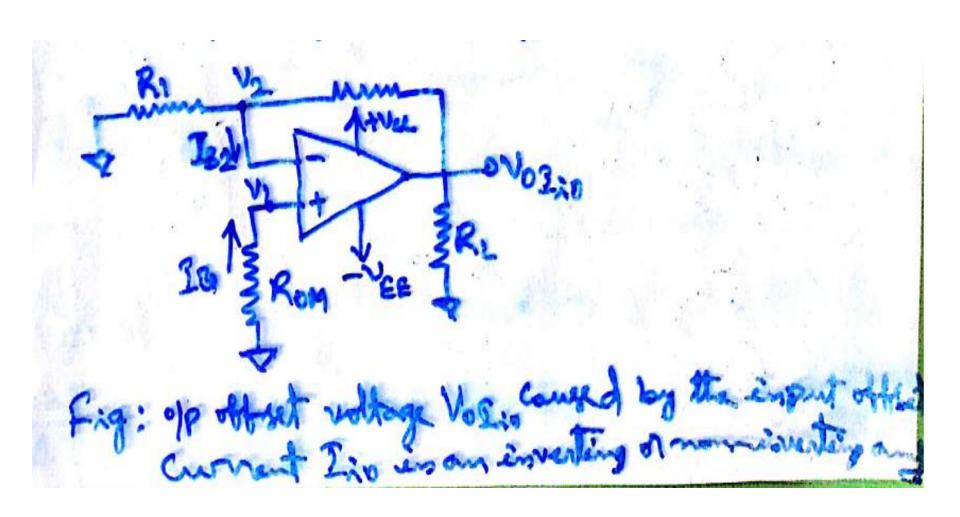

#### Input offset Current:

The input offset current lio is defined as the algebraic difference between two input bias currents lb1 and lb2. In equation form it is

$$lio = |lb1 - lb2|$$

#### Input Bias Current:

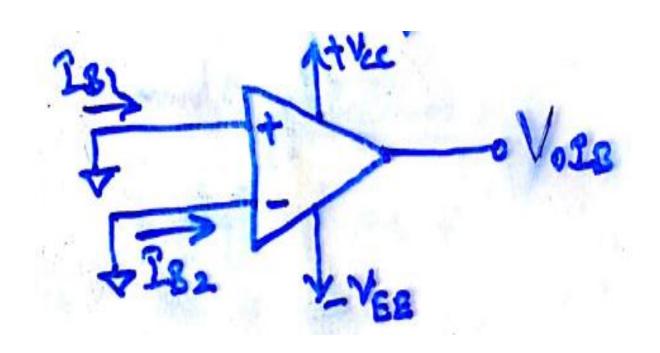

An input bias current Ib is defined as the average of the two input bias currents, Ib1 and Ib2 as shown in the following figure.

Ib = (Ib1 + Ib2)/2 [Ib – DC current]

Where Ib1= DC bias current flowing into the noninverting input

Ib2 = DC bias current flowing into the inverting input

- The value of input bias current Ib is very small, in the range of a few to few hundred nano amp.

#### Thermal Drift:

- The average rate of change of input offset voltage per unit change in temperature is called thermal voltage drift, and is denoted by  $\Delta Vio/\Delta T$ . Units  $\mu V/^{\circ}C$

- Similarly, the thermal drift in the input offset current

& input bias current are defined as follows.

- $-\Delta lio/\Delta T$ = thermal drift in input offset current(pA/°C)

- $\Delta Ib/\Delta T$ = thermal drift in input bias current(pA/°C)

- Supply Voltage Rejection Ratio (SVRR) or Power Supply Rejection Ratio (PSRR):

- The change in op-amp's input offset voltage caused by variations in the supply voltages is called Supply voltage Rejection Ratio or Power Supply Rejection Ratio.

- This is expressed either in microvolts per volt or in decibles

- For example, SVRR for  $\mu A_{74^{1}}$  is  $\Delta Vio/\Delta V = 150 \mu V/V$  maximum and it is 76.48 in DB.

#### Common Mode Rejection Ratio (CMRR):

- It can be defined as the ratio of the differential gain AD to the common mode gain Acm, that is CMRR = Ad/Acm

- It is a measure of the degree of matching between two input terminals, that is, the larger the value of CMRR, the better is the matching between the two input terminals and the smaller is the output common mode voltage Vocm.

#### Differences b/w Ideal and Practical Op-Amp

| Characteristics                           | Ideal Op-amp | Practical Op-amp |

|-------------------------------------------|--------------|------------------|

| Voltage gain                              | Infinite     | High             |

| Input resistance                          | Infinite     | High             |

| Output resistance                         | Zero         | Low              |

| Output voltage when input voltage is zero | Zero         | Low              |

| Band width                                | Infinite     | High             |

| CMRR                                      | Infinite     | High             |

| Slew Rate                                 | Infinite     | High             |

#### Characteristics of Op-amp

- DC Characteristics: DC Characteristics include input bias current, input offset current, Input offset voltage, Output offset voltage and Thermal drift.

- AC Characteristics: AC characteristics include

- Frequency Response

- Slew Rate

#### Frequency Response:

- Ideally an op-amp should have an infinite band width.

- The practical op-amp gain, however, decreases at higher frequencies.

- What is the cause for the gain of the op-amp to roll-off after certain frequency is reached?

- Obviously, there must be a capacitive component in the equivalent circuit of the op-amp. This capacitace is due to the physical characteristics of the device(BJT or FET) used and internal construction of op-amp.

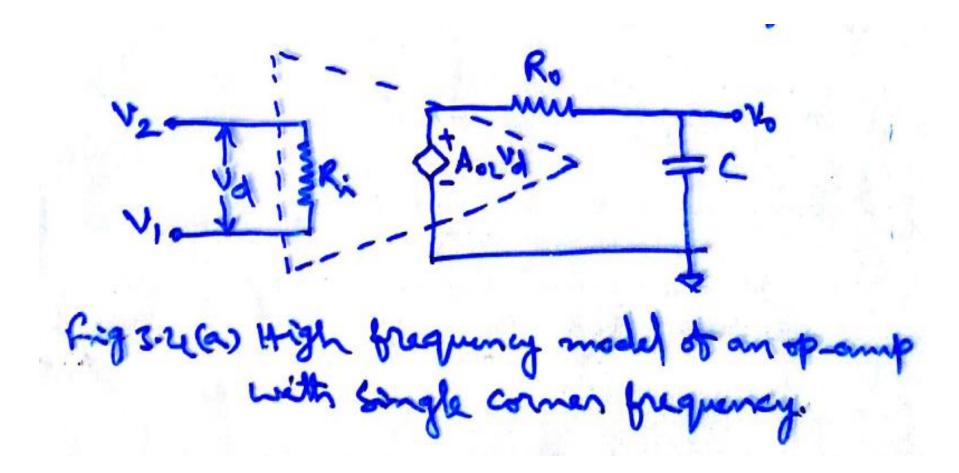

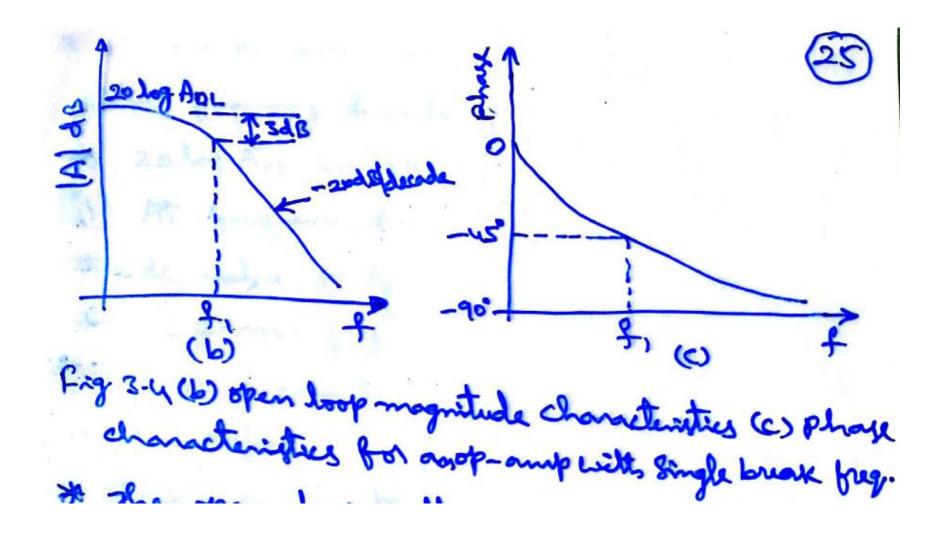

- For an op-amp with only one break frequency, all the capacitor effects can be represented by a single capacitor C as shown in figure 3.4 (a).

The open loop voltage gain of an op-amp with only one corner frequency is obtained from Figure 3.4(a) as

```

Vo = -j Xc/(Ro-jXc) AolVd

=> A = Vo/Vd = Aol/(1+j2\pifRoC)

A = Aol/(1+jf/f1) where f1 = 1/2\pi Ro C

```

• f1 is the corner frequency or the upper 3 dB frequency of the op-amp.

The magnitude and the phase angle of the open loop voltage gain are function of frequency and can be written as

$$|A| = Aol/(v(1+(f/f1)^2))^{-\phi} = -tan-1(f/f1)$$

these are shown in Fig 3.4(b) and 3.4 (c)

- It can be seen that

- For frequency f<<f1, the magnitude of the gain is 20 log</li>

Aol in dB.

- At frequency f = f1, the gain is 3 dB down from the DC value of AoI in dB. This frequency f1 is called corner frequency

- For f>>f1, the gain rolls off at the rate of -20dB/decade.

- It can further be seen from the phase characteristics that the phase angle is zero at frequency f=0.

- At corner frequency f1, the phase angle is -45° and at infinite frequency the phase angle is -90°. This shows that a maximum of 90° phase change can occur in an op-amp with a single capacitor.

#### Slew Rate:

- The slew rate is defined as the maximum rate of change of output voltage per unit of time and is expressed in volts per micro seconds. In equation form, SR = (dVo/dt)|maximum V/μs.

- Slew rate indicates how rapidly the output of an opamp can change in response to changes in the input frequency.

- One of the drawbacks of the 741C is it's low slew rate(0.5 V/μs), which limits its use in relatively high frequency applications, especially in oscillators, comparators and filters

- In high-speed op-amps especially, the slew rate is significantly improved. For instance, the LM138 has a slew rate of 70 V/ $\mu$ s.

- What causes the slew rate? There is usually a capacitor with in or outside an op-amp to prevent oscillation. It is this capacitor which prevents the output voltage from responding immediately to a fast changing input.

- The rate at which the voltage across the capacitor Vc increases is given by dVc/dt = I/C. Here, I is the maximum current furnished by op-amp to the capacitor C. This means that for obtaining faster slew rate, op-amp should have either a higher current or a small compensating capacitor.

- For the 741C, that maximum internal capacitor charging current is limited to about 15  $\mu$ A. So the slew rate of 741C is SR = dVc/dt|max = Imax/C = 15  $\mu$ A/30 PF = 0.5 V/  $\mu$ s.

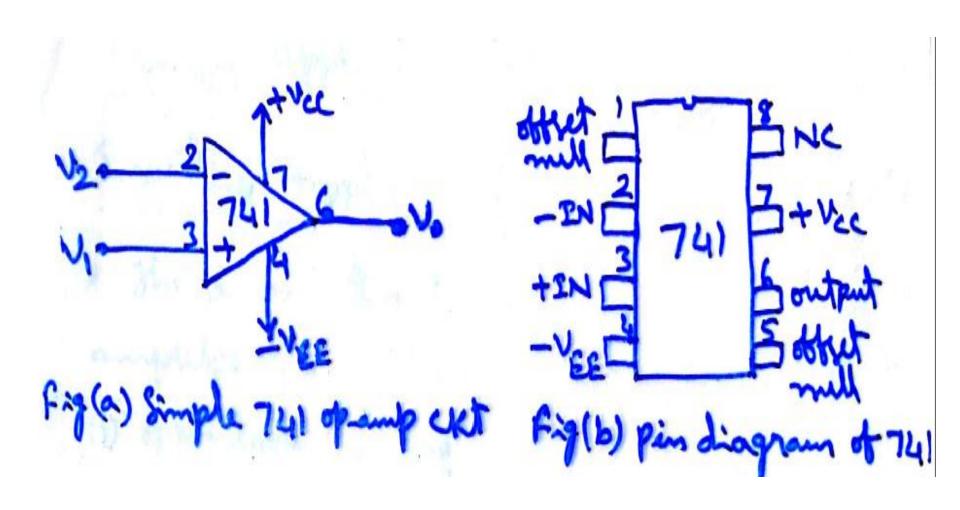

# 741 Op-amp and it's features

#### 741 Op-amp and it's features cntd...

• The μA741 is a high performance monolithic operation amplifier constructed using the planar epitaxial process.

The op-amp features are given below

- 1. High common mode voltage range make the  $\mu$ A741 ideal for use as voltage follower.

- 2. The high gain and wide range of operating voltage provides superior performance in integrator, summing amplifier, and general feedback applications.

- 3. 741 is internally frequency compensated op-amp

- 4. 741 is available in all 3 packages viz 8-pin metal can, 10-pin flat pack, and 8 or 14 pin DIP.

- 5. Offset voltage null capability is available.

- 6. It consumes low power

#### Modes of Op-amp

- Basically there are 2 modes of op-amp. They are

- Inverting Amplifier

- Non-Inverting Amplifier

#### **Inverting Amplifier**

- There are two types of connecting inverting amplifier. They are

- Open loop inverting amplifier

- Closed loop inverting amplifier

### Modes of Op-amp cntd...

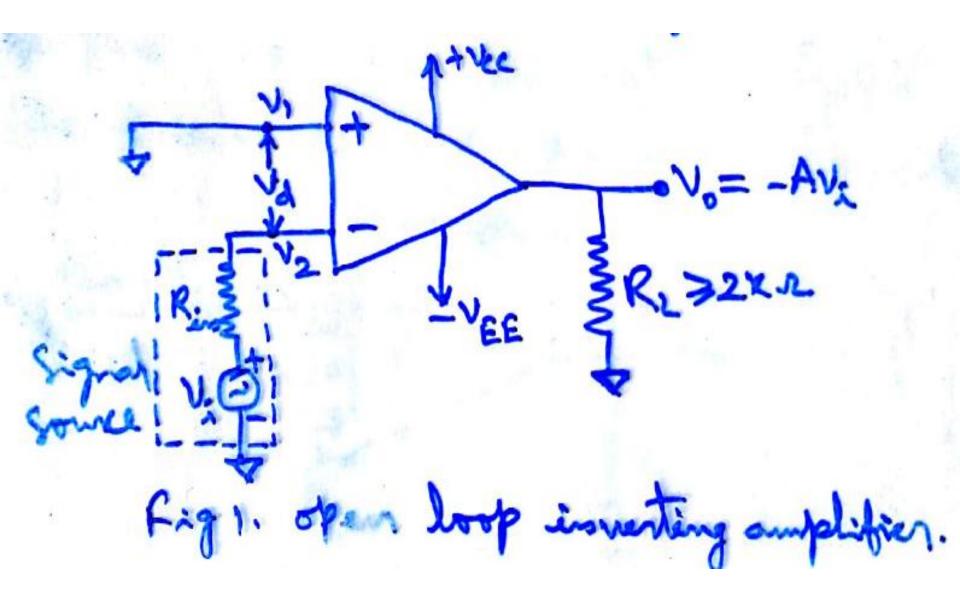

#### **Open Loop Inverting Amplifier**

The circuit diagram for the open loop inverting amplifier is shown in figure 1.

# Modes of Op-amp cntd...

#### Modes of Op-amp cntd..

The equation for the output voltage is given by

$$Vo = A(V1 - V2)$$

where A – large signal voltage gain

V1 – voltage at non-inverting input terminal

V2 – voltage at inverting input terminal

here V1 = 0 and V2 = Vi therefore

$$Vo = A (-Vi) = - A Vi$$

- The negative sign indicates that the output voltage is out of phase with respect to the input by 180° or is of opposite polarity.

- Thus in the inverting amplifier the input signal is amplified by gain A and is also inverted at the output.

#### Modes of Op-amp cntd..

#### **Closed Loop Inverting amplifier**

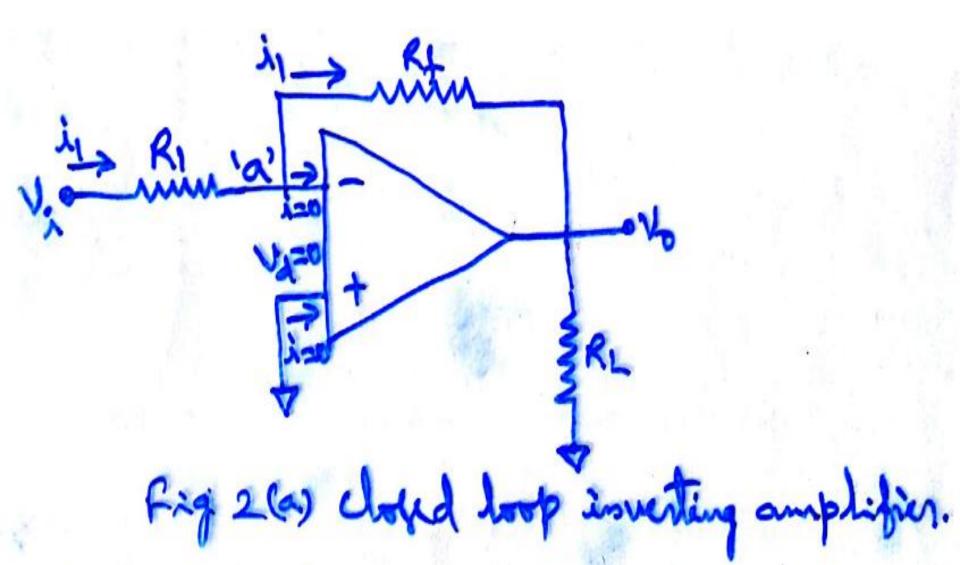

- This is perhaps the most widely used of all the op-amp circuits.

- The circuit is shown in the figure 2(a)

# Modes of Op-amp cntd..

- For simplicity, assume ideal op-amp. As Vd=0, node 'a' is at ground potential and the current i1 through R1 is i1 = Vi/R1

- Also since op-amp draws no current, all the current flowing through R1 must flow through Rf. Hence the output voltage is

$$Vo = -i1 Rf = -(Vi/R1) Rf$$

- therefore the gain of the closed loop inverting amplifier is Acl = Vo/Vi = -Rf/R1

- The –ve sign indicates a phase shift of 180° between Vi and Vo.

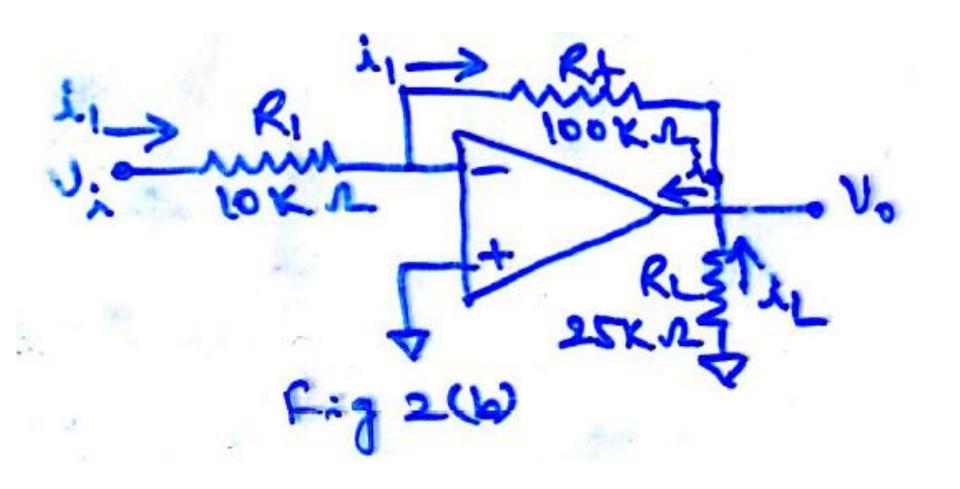

#### **Example:**

• In figure 2(b), R1 =  $10K\Omega$ , Rf =  $100K\Omega$ , Vi=1v. A load of 25  $K\Omega$  is connected at the output terminal. Calculate (i) I1 (ii) V0 (iii) il and total current io into the output pin

(i)

$$i1 = Vi/R1 = 1V/10K\Omega = 0.1 \text{ mA}$$

(ii)  $Vo = -Rf/R1 \text{ Vi} = -10V$

(iii)  $il = -Vo/Rl = 10V/25 \text{ K}\Omega = 0.4 \text{ mA}$

Therefore  $I_0 = i1 + il = 0.1 \text{ mA} + 0.4 \text{ mA} = 0.5 \text{ mA}$

### **Non-Inverting Amplifier:**

- There are two types of connecting noninverting amplifiers. They are

- Open loop non-inverting amplifier

- Closed loop non-inverting amplifier

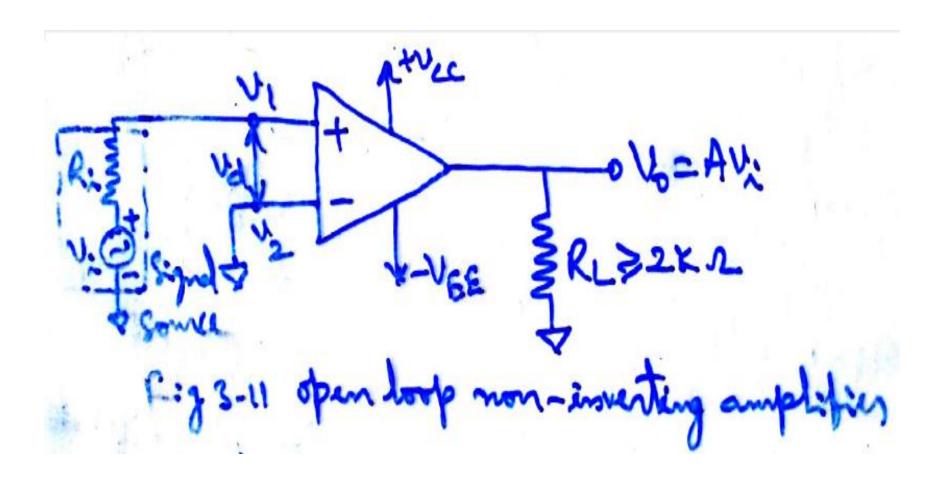

### **Open Loop Non-inverting amplifier**

Figure 3.11 shows the open loop non-inverting amplifier

- Output voltage, Vo = A (V1 V2)

here V1 = Vi and V2 = 0 v

therefore Vo = A Vi

- This means that the output voltage is larger than the input voltage by gain A and is in phase with the input signal.

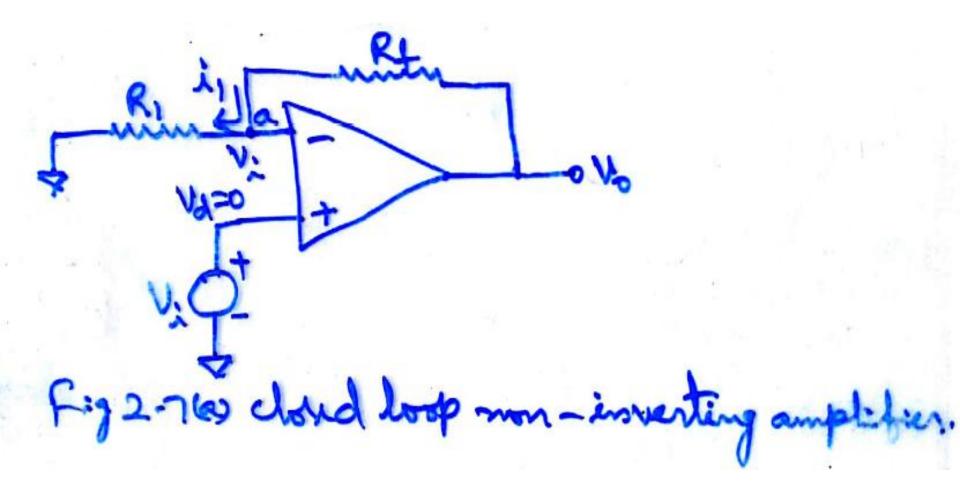

### **Closed Loop Non-Inverting Amplifier:**

If the signal is applied to the non-inverting input terminal and feedback is given as shown in Figure 2.7(a), the circuit amplifies without inverting the input signal. Such a circuit is called non-inverting amplifier.

- As Vd=0, the voltage at node 'a' in Figure 2.7(a) is Vi. Now R1 and Rf forms a potential divider.

- Hence Vi = (Vo/(R1+Rf)) \* R1 as no current flows into op-amp.

- therefore Vo/Vi = (R1+Rf)/R1 = 1+ (Rf/R1)

- Thus, for non-inverting amplifier the voltage gain

Acl = Vo/Vi = 1 + (Rf/R1)

- The gain can be adjusted to unity or more, by proper selection of resistors Rf and R1.

### **Difference Amplifier:**

Figure 4.14 shows the diagram of difference amplifier

A close examination of the figure 4-14 reveals that difference amplifier is a combination of inverting and non-inverting amplifiers i.e. when Vx = 0, circuit is a non-inverting amp.

when Vy = 0, circuit is an inverting amp.

#### **Voltage Gain:**

The circuit in the figure 4-14 has two inputs Vx and Vy. Therefore we use super position theorem in order to establish the relation ship between inputs and output.

```

When Vy = 0, the output voltage due to Vx only is

Vox = -(Rf/R1) Vx ----- eq(1)a

Similarly when Vx=0, the configuration is a non-

inverting amplifier having a voltage divider network

composed of R2 and R3 at the non-inverting input.

Therefore V1 = (R3/R2+R3)(Vy)

the output due to Vy alone is

Voy = (1 + Rf/R1) V1 \rightarrow

Voy = (R1 + Rf)/R1 (R3/R2 + R3) Vy

Since R1 = R2 and Rf = R3, Voy= (Rf/R1) (Vy) ---- eq(1)b

```

- Thus from equations (1)a and (1)b, the net output voltage is Vo = Vox + Voy

- → Vo= (-Rf/R1) (Vx Vy) = (Rf/R1) Vxy therefore the voltage gain Ad=Vo/Vxy = -Rf/R1

- Note that the gain of the difference amplifier is the same as that of the inverting amplifier.

#### **Input Resistance:**

The input resistance Rif of the difference amplifier is the resistance determined looking into either one of the two input terminals with the other grounded

- Therefore with Vy = 0, the input resistance of the inverting amplifier is Rifx = R1 ----- eq(2)a

- Similarly with Vx=0, the input resistance of non-inverting amplifier is Rify =R2+R3 --eq(2)b

- Therefore from eqs 2a and 2b, it is obvious that the input resistances seen by the signal sources Vx and Vy are not the same.

- **Example:** In the circuit of figure 4-14, R1=R2=1K $\Omega$ , Rf=R3=10K $\Omega$ , and the op-amp is a 741C, a) what are the gain and input resistance of the amplifier?

- (b) Calculate the output voltage Vo if Vx=2.7 Vpp and Vy= 3 Vpp sine waves at 100Hz.

- **Solution:** (a) Ad= -Rf/R1=-10K $\Omega$ /1K $\Omega$  = -10 Rifx = R1 = 1K $\Omega$  and Rify = R2 + R3 = 11K $\Omega$

- (b) Output voltage Vo= Ad Vxy = Ad(Vx-Vy) = -10(2.7 - 3) = -10(-0.3) = 3 V peak to peak sine wave at 100Hz.

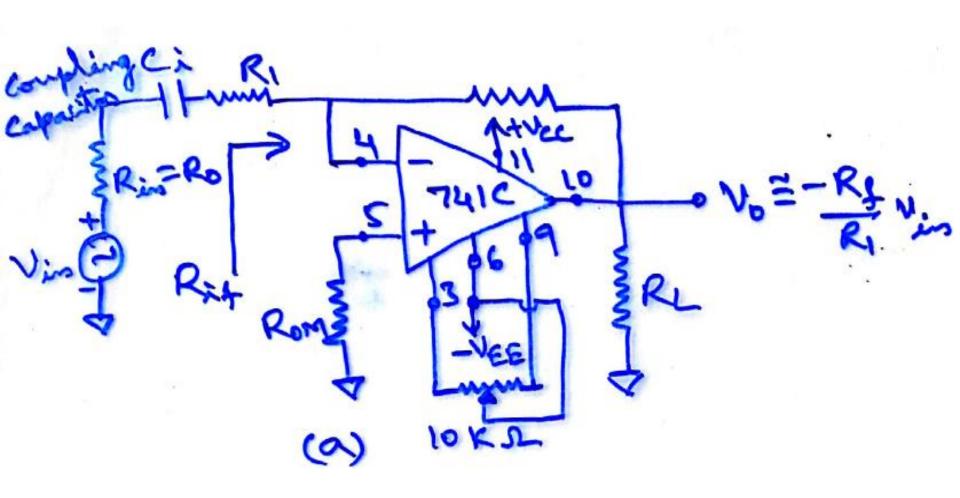

# **AC Amplifier**

- If an AC input is riding on some DC level, it is necessary to use an AC amplifier with a coupling capacitor to block the DC amplification.

- For example, in an audio receiver system that consists of a number of stages, because of thermal drift, component tolerances, and variations the DC level is produced.

- To prevent the amplification of such DC levels, the coupling capacitors must be used between the stages.

- The figure 7-3 shows the AC inverting and noninverting amplifiers with coupling capacitors.

The coupling capacitor not only blocks the DC voltage but also set the low frequency cut off limit which is given by

$$fL = 1/2\pi Ci(Rif+Ro)$$

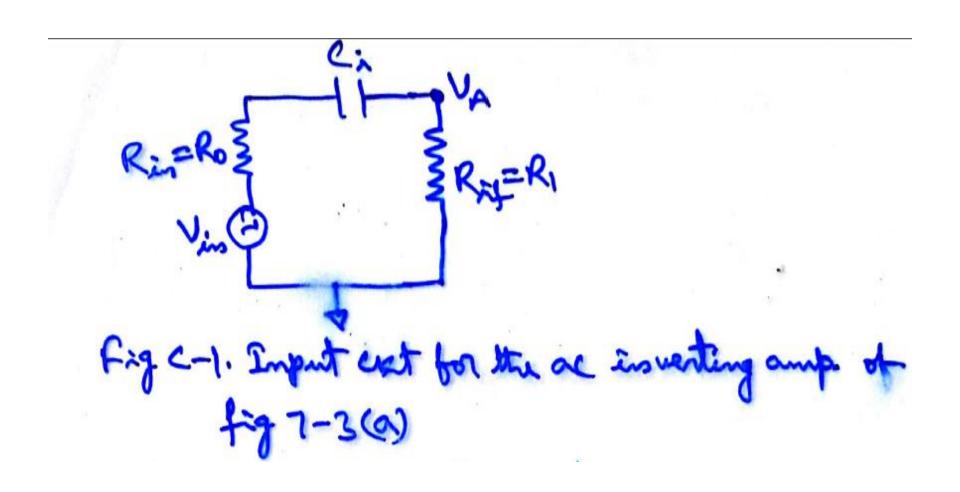

#### **Derivation of fL:**

• The input circuit of AC inverting amplifier of Figure 7-3a is drawn in figure C-1.

- The voltage VA is amplified by the AC inverting amplifier, hence it is necessary to determine VA as a function of input voltage Vin

- Using voltage divider rule, we get

```

VA = Rif Vin/(Ro + 1/jwCi + Rif) ----- eq(1)

```

where Rif – input resistance of inverting amplifier

Ro – Source resistance, Rin

Rearranging eq (1)

```

VA = j (Rif w Ci) Vin/j(Rif + Ro) w Ci + 1

= j (2\pi f Ci Rif) (Vin) / j ((2\pi f Ci)(Rif+Ro) + 1)

```

```

VA = j(2πf Ci Rif) (Vin)/(j(f/fL)+1)

where f – Input frequency (Hz)

fL = 1/2π Ci(Rif + Ro)

where fL = low frequency cut-off or low end of bandwidth

Ci= DC blocking capacitor

```

Rif = AC input resistance of second stage

Ro = AC output resistance of 1<sup>st</sup> stage or Rin

The high end of the bandwidth is given by

$$fH = UGB(K)/|AcI|$$

where UGB – Unity gain bandwidth = 10<sup>6</sup>

K = 0.909 = Constant factor

Acl = closed loop gain

Therefore bandwidth of the amplifier is

$$BW = fH - fL$$

- The Resistor Rom is used to minimize the effect of output offset voltage

- Since the reactance of Ci is negligible with in the bandwidth, the closed loop gain of the AC inverting amplifier is Acl = -Rf/R1

- And the closed loop gain of the AC non-inverting amplifier is

$$Acl = 1 + Rf/R1$$

Example : in the circuit of Fig 7.3(a) Rin=50 $\Omega$ , Ci= 0.1  $\mu$ F, R1=100  $\Omega$ , Rf= 1 K $\Omega$ , Rl=10K $\Omega$  and supply voltages=+ or – 15 V. Determine the bandwidth of the amplifier

```

Solution: Band width = fH – fL

where fH = (UGB)(K)/|Acl|

Acl = -Rf/R1 = -1K\Omega / 100 \Omega = -10

therefore fH = 10^6(0.909)/10 = 90.9 \text{ KHz} and

fL= 1/2\pi Ci(Rif+Ro)

where Rif = input resistance of the inverting amplifier

with feedback

Rif=R1=100\Omega

Ro= Source resistance = Rin = 50 \Omega

therefore fL= 1/2\pi (10^{-7}) (100+50) = 10.6 \text{ KHz}

Therefore bandwidth = 90.9 \text{ KHz} - 10.6 \text{ KHz} = 80.3 \text{ KHz}

```

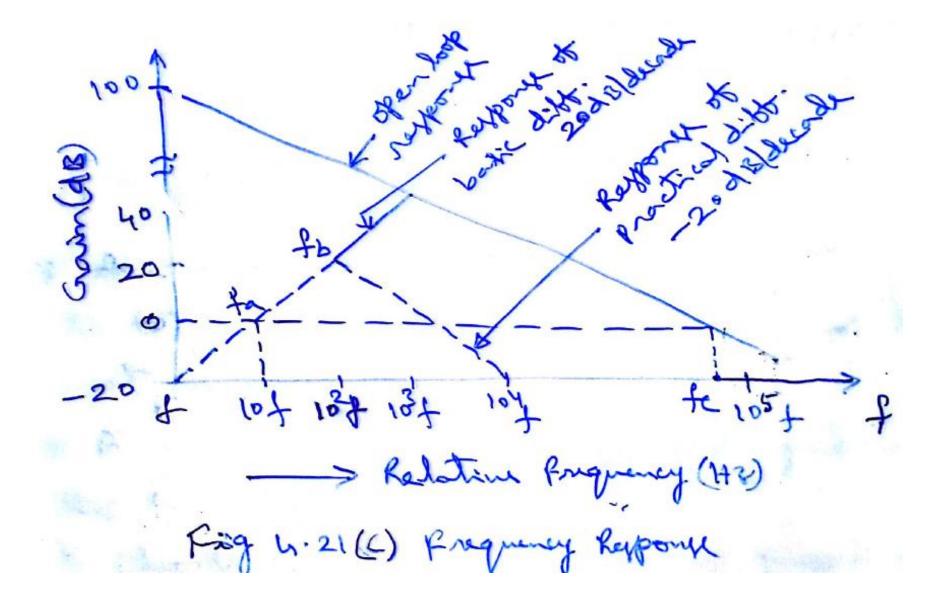

## Differentiator

#### **Differentiator:**

A differentiator is a circuit in which the output waveform is the derivative of input waveform.

A differentiator circuit is shown in the figure 4.21(a).

#### **Analysis:**

- The node N is at virtual ground potential ie Vn=0. The current ic through the capacitor is ic= C1 d(Vi-Vn)/dt = C1 dVi/dt

- The current If(not the English word if) through the feedback resistor = Vo/Rf and there is no current into the op-amp

Therefore nodal equation at node N is

$$C1 dVi/dt + Vo/Rf = 0$$

The minus sign indicates a 180° phase shift of the output waveform Vo with respect to the input signal.

The phasor equivalent of equation (1). is

Vo(s) = - Rf C1 S Vi(s) where Vo & Vi are the phasor representation of vo & vi.

In steady state put s=jw. Now the magnitude of gain A of the differentiator is

|A| = |Vo/Vi| = |-jw Rf C1| = w Rf C1 ---- eq(2)

Eq (2) may be written as

|A| = f/fa where  $fa = 1/2\pi Rf C1$

At f = fa, |A| = 1 ie = 0 dB, and the gain increases at a rate of +20dB/decade.

Thus at high frequency, a differentiator may become unstable and break into oscillations.

- There is one more problem in the Differentiator of figure 4.21(a).

- The input impedance (ie 1/wC1) decreases with increase in frequency there by making the circuit sensitive to high frequency noise.

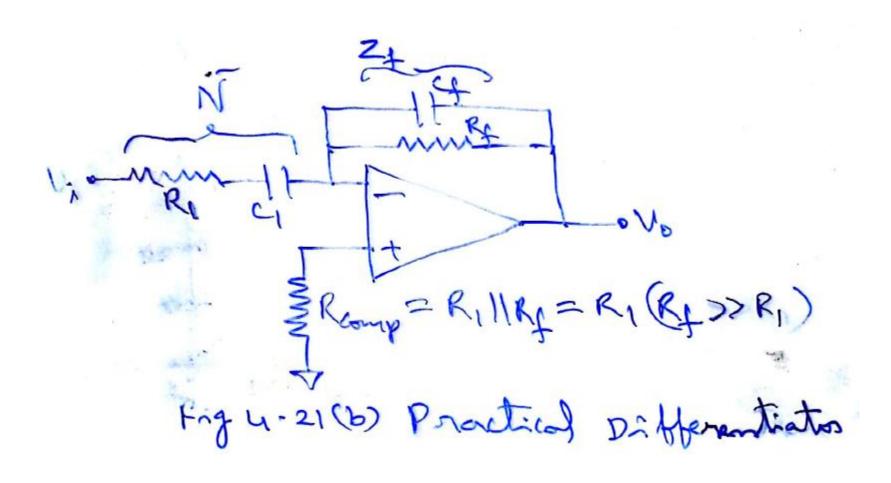

#### **Practical Differentiator:**

A practical differentiator of the type shown in Figure 4.21b eliminates the problem of stability and high frequency noise.

```

The transfer function for the circuit in Figure 4.21b is

mentioned as

Vo(s)/Vi(s) = -Zf/Zi = -sRfC1/(1+sRfCf)(1+sR1C1)

For RfCf = R1C1, we get

Vo(s)/Vi(s) = -sRfC1/(1+sR1C1)^2

=-sRfC1/(1+if/fb)^2 ---- eq(3)

where fb=1/2\pi R1C1

from eq(3), it is evident that the gain increases at +20

dB/decade for frequency f < fb and decreases at -20

dB/decade for f > fb as shown by dashed lines in figure

4.21(c)

```

- This 40 dB/decade change in gain is caused by R1C1 and RfCf factors.

- For the basic differentiator of Fig.4.21(a) the frequency response would have increased continuously at the rate of +20dB/decade even beyond fb causing stability problem at high frequency.

- Thus the gain at high frequency is reduced significantly, thereby avoiding the high frequency noise and stability problems.

- The value of fb should be selected such that

where fc is the unity bandwidth of the op-amp in open loop configuration.

#### Differentiator cntd...

- A resistance Rcomp is normally connected to the (+) input terminal to compensate for the input bias current.

- A good differentiator may be designed as per the following steps.

- 1. Choose fa equal to the highest frequency of the input signal. Assume a practical value of C1 (< 1  $\mu$ F) and then calculate Rf fa = 1/2 $\pi$  Rf C1

- 2. Choose fb = 10 fa (say). Now calculate the value of R1 from fb =  $1/2\pi$  R1 C1 and Cf so that

$$R1C1 = RfCf$$

#### Differentiator cntd...

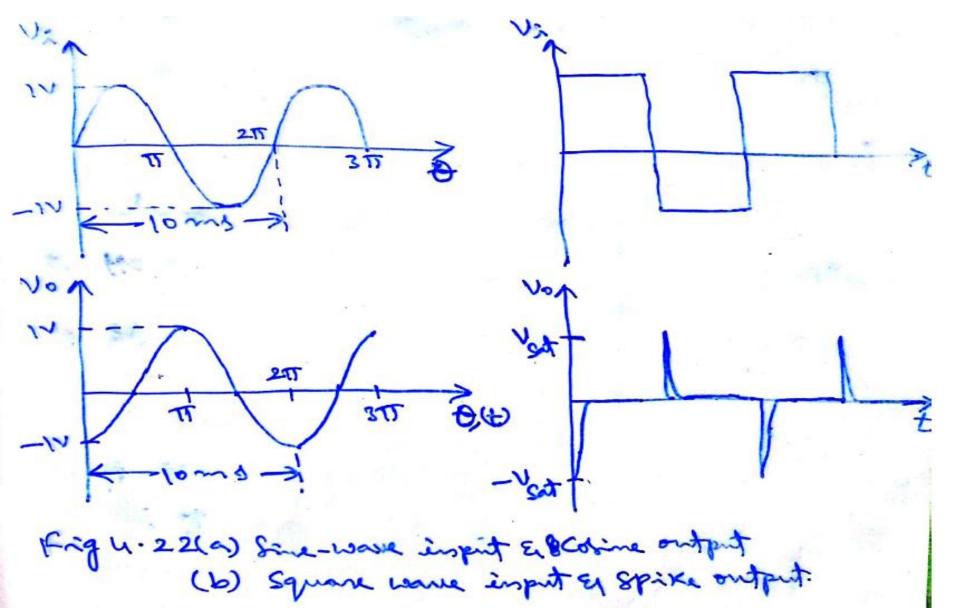

- Example: (a) Design an op-amp differentiator that will differentiate an input signal with fmax = 100 Hz.

- (b) Draw the output waveform for a sine wave of 1V peak at 100 Hz applied to the differentiator(c) Repeat part (b) for a square wave input.

#### Differentiator cntd..

#### Solution:

```

a) Select fa = fmax = 100 \text{ Hz} = 1/2\pi \text{ Rf C1}

let C1 = 0.1 \mu F

Then Rf = 1/2\pi(10^2)(10^-7) = 15.9 \text{ K}\Omega

Now choose fb = 10 fa = 10 (100 Hz) = 1 KHz

= 1/2\pi R1 C1

Therefore R1 = 1/2\pi (10<sup>3</sup>)(10<sup>-7</sup>) = 1.59 KΩ

since Rf Cf = R1 C1

We get Cf = 1.59 (10<sup>3</sup>) (10<sup>-7</sup>)/15.9(10<sup>3</sup>) = 0.01\muF

```

#### Differentiator cntd...

```

(b) Vi = 1 \sin 2\pi (100) t

from eq (1), Vo = -Rf C1 dVi/dt

Vo = -(15.9 K\Omega) (0.1 \muF) d[1 v sin 2\pi (10^2) t] /dt

= -(15.9 K\Omega) (0.1 \muF) 2\pi (10^2) cos[2\pi(100)t]

= -0.999 \cos[2\pi (100) t]

= -1 \cos[2\pi (100) t]

The input and output waveforms are shown in

```

Figure 4.22

#### Differentiator cntd..

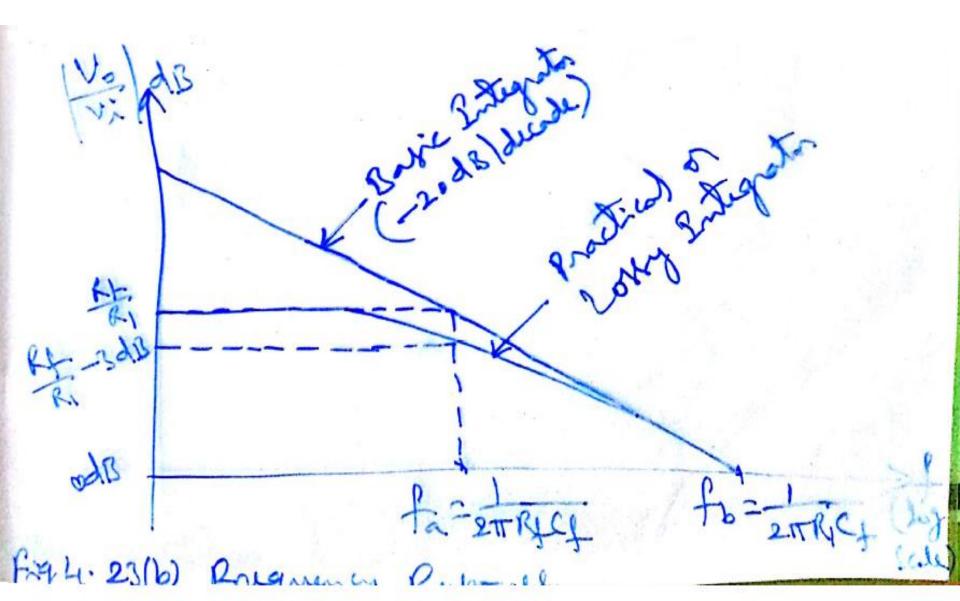

### Integrator

By interchanging the resistor and capacitor of the Differentiator, we get the circuit of an integrator which is shown in the figure 4.23(a).

#### Integrator

cntd..

- The nodal equation at node N is (Vi/R1) + Cf dVo/dt = 0

- $\rightarrow$  dVo/dt = -(1/R1 Cf) Vi

- →<sub>0</sub>∫<sup>t</sup> dVo = (-1/R1Cf)<sub>0</sub>∫<sup>t</sup> Vidt Vo(t)= (-1/R1Cf)<sub>0</sub>∫<sup>t</sup> Vi(t)dt + Vo(0) ----- eq(1) where Vo(0) is the initial o/p voltage.

- Here R1Cf is the time constant of the integrator

- Here –ve sign is present, hence it is called inverting integrator.

- Rcomp is the resistor to minimize the effect of input bias current.

- The operation of the integrator can also be studied in the frequency domain. In phasor notation the equation (1) can be written as

$$Vo(s) = -(1/sR1Cf) Vi(s)$$

In steady state, put s=jw and we get

$$Vo(jw) = - (1/jwR1Cf) Vi(jw)$$

So the magnitude of the gain is

$$|A| = |Vo(jw)/Vi(jw)| = |-1/jwR1Cf|$$

= 1/wR1Cf = 1/(f/fb)

Where  $fb = 1/2\pi R1Cf$

The frequency response is shown in the figure 4.23b

# Integrator

cntd..

## Integrator

#### cntd..

- The Bode plot of basic integrator is a straight line of slope -20 dB/decade.

- The frequency fb is the frequency at which the gain of the integrator is 0 dB and is given by

$$fb = 1/2\pi R1Cf$$

As the gain of the integrator decreases with increasing frequency, the integrator circuit does not have any frequency problem as faced in the differentiator. However, at low frequencies such as DC (w=0), the gain becomes infinite (ie saturates). The solution to this problem is a practical integrator circuit.

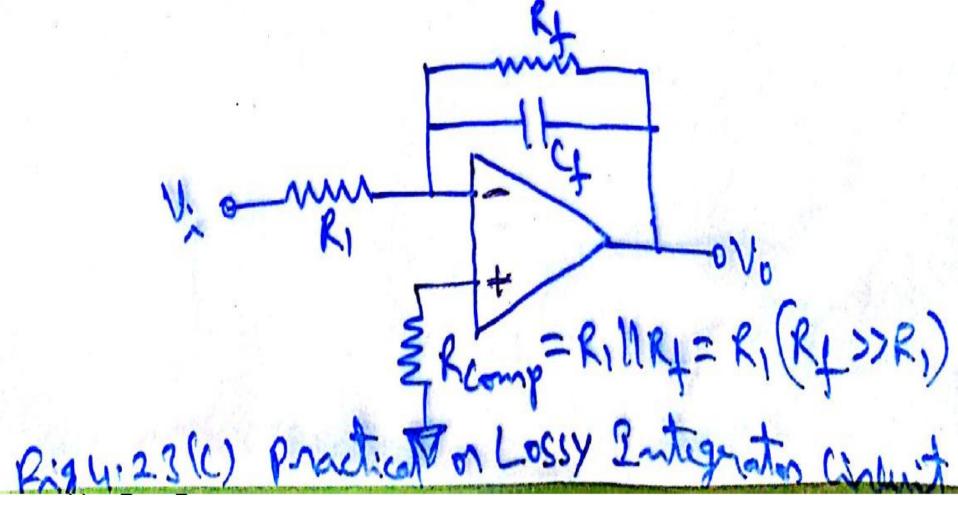

#### **Practical Integrator Circuit (Lossy Integrator):**

The gain of an integrator at low frequency (DC) can be limited to avoid the saturation problem if the feedback capacitor is shunted by a resistance Rf as shown in the Figure 4.23c

- The parallel combination of Rf and Cf behaves like a practical capacitor which dissipates power unlike an ideal capacitor. For this reason, this circuit is also called as a Lossy integrator.

- The resistor Rf limits the low frequency gain to

Rf/R1 (generally Rf = 10 R1) and thus

provides DC stabilization.

## Integrator

#### cntd..

#### **Analysis:**

The nodal equation at the inverting input terminal of the op-amp is

$$Vi(s)/R1 + sCf Vo(s) + Vo(s)/Rf = 0$$

From which we have

$$Vo(s) = -(1/(sR1Cf + R1/Rf)) Vi(s)$$

- If Rf is large, the lossy integrator approximates the ideal integrator.

- For S=jw, the magnitude of the gain of Lossy integrator is given by

```

|A| = |Vo/Vi| = 1/(\sqrt{w^2R1^2 Cf^2 + R^2/Rf^2})

= Rf/R1/(\(\(\frac{1}{(wRf Cf)^2)} ----- eq(2)

```

- The Bode plot of the Lossy Integrator is also shown in the Figure 4.23b. At low frequencies the gain is constant at Rf/R1.

- The break frequency (f = fa) at which the gain is 0.707 (Rf/R1) is calculated from eq (2) as

$$\sqrt{(1+ \text{ w Rf Cf})^2} = \sqrt{2}$$

$$\rightarrow$$

wRf Cf = 1  $\rightarrow$  f = 1/2 $\pi$ Rf Cf

solving for

$$f = fa$$

, we get  $fa = 1/2 \Pi Rf Cf$

This frequency tells us where the useful integration range starts in Figure 4.23b

- If the input frequency is lower than fa, the circuit acts like a simple inverting amplifier and no integration results.

- At the input frequency equal to fa, 50% accuracy results.

- The practical thumb rule is that if the input frequency 10 times fa, then 99% accuracy can result.

## Comparator

- A comparator is a circuit which compares a signal voltage applied at one input of an op-amp with a known reference voltage at the other input.

- There are basically two types of comparators.

- 1. Non-inverting comparator

- 2. Inverting comparator

#### **Non-Inverting Comparator:**

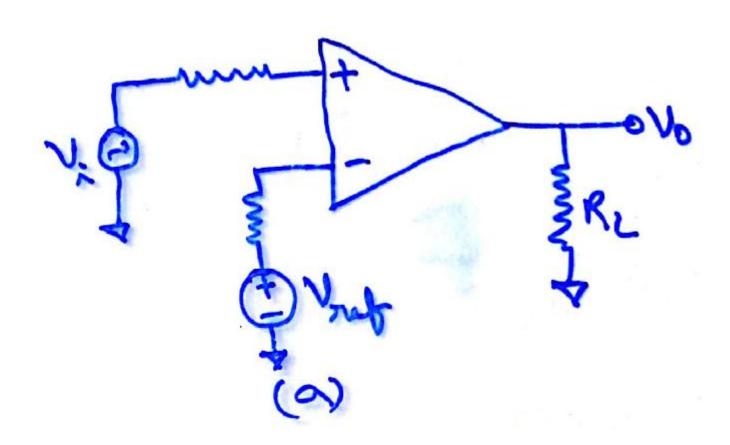

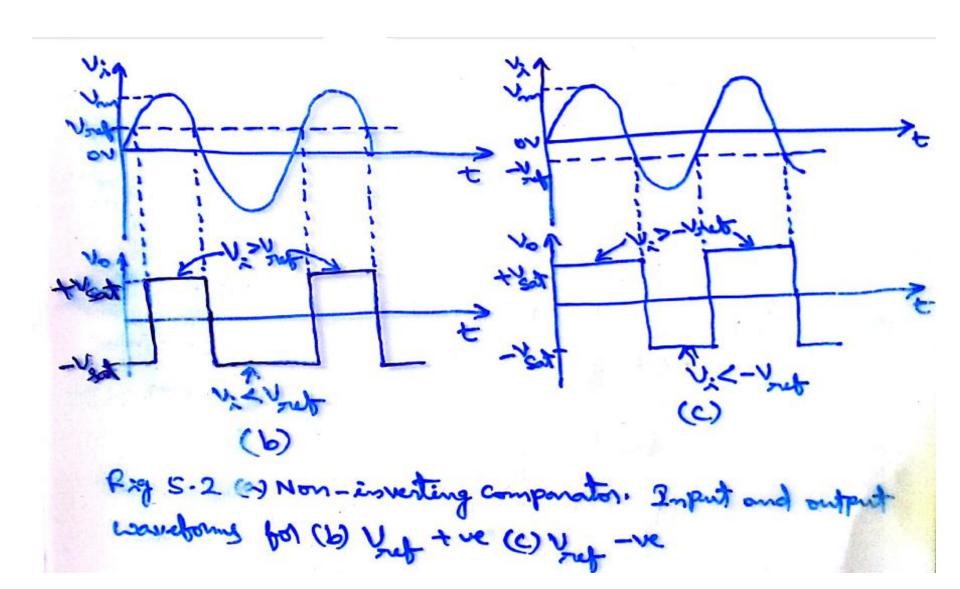

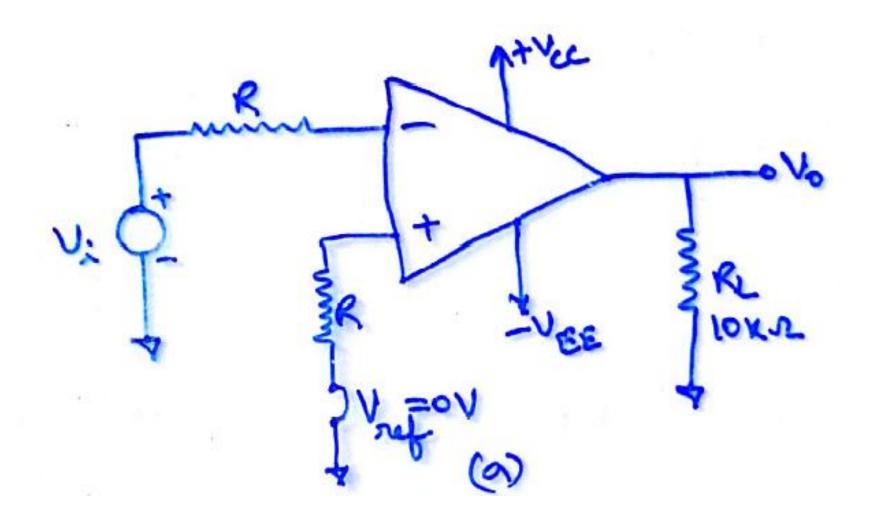

- The circuit of figure 5.2a is called a non-inverting comparator.

- A fixed reference voltage Vref is applied to

input and a time varying signal Vi is applied to

input.

- There are 3 conditions for a comparator. They are Vi < Vref → Vo = -Vsat</li>

- $Vi > Vref \rightarrow Vo = +Vsat$

- $Vi = Vref \rightarrow changes the state of op-amp$

The output waveform for a sinusoidal input signal applied to the +ve input is shown in figure 5.2 (b) and (c) for +ve and –ve Vref respectively.

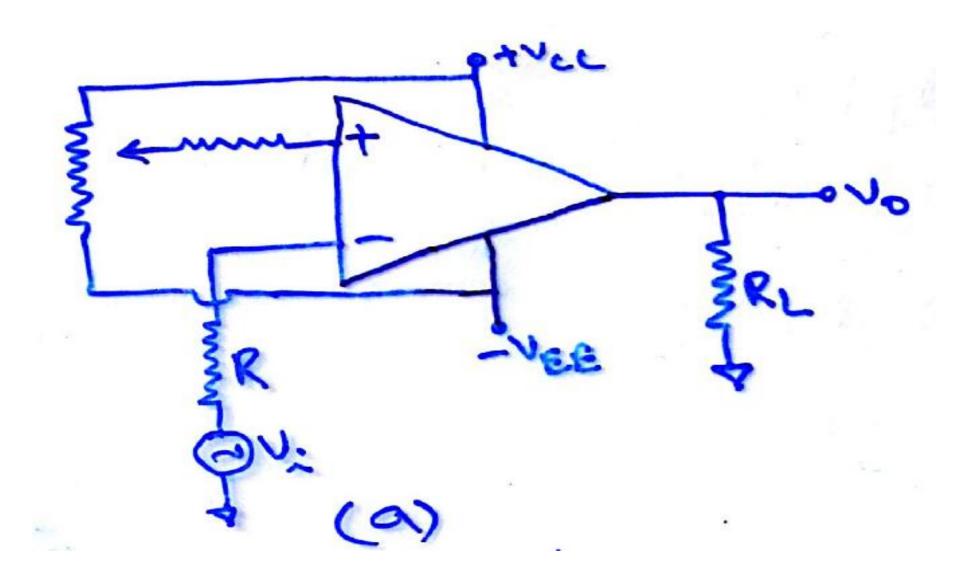

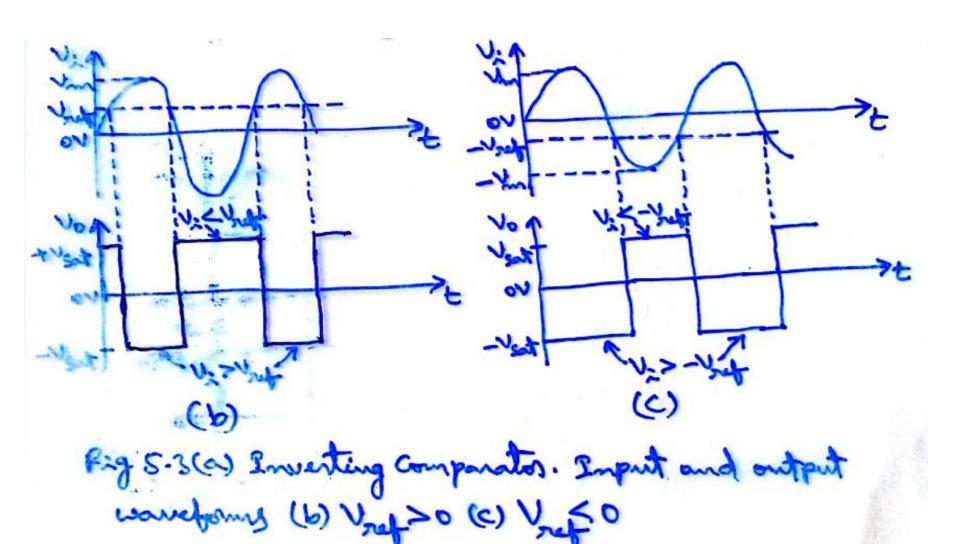

#### **Inverting Comparator:**

- Figure 5.3(a) shows a practical inverting comparator in which the reference voltage

Vref is applied to the +input and Vi is applied to the –ve input.

- For a sinusoidal input signal, the output waveform is shown in in figure 5.3(b) and 5.3(c) for Vref +ve and –ve respectively.

## **Applications of Comparator**

- Some important applications of comparator are

- Zero crossing detector

- Window detector

- Time marker generator

- Phase meter.

# Zero crossing detector

# Zero crossing detector cntd..

2 ig 5-4 (a) Zero crossing detector (b) Emput and ofp waveform

### Zero crossing detector cntd..

- The basic comparators either non-inverting or inverting can be used as a zero crossing detector provided that Vref is set to zero. An inverting zero-crossing detector is shown in figure 5.4 (a).

- The input and output waveforms are shown in Figure 5.4 (b).

- The circuit is also called as a sine to square wave generator.

- If positive feedback is added to the comparator circuit, gain can be increased greatly.

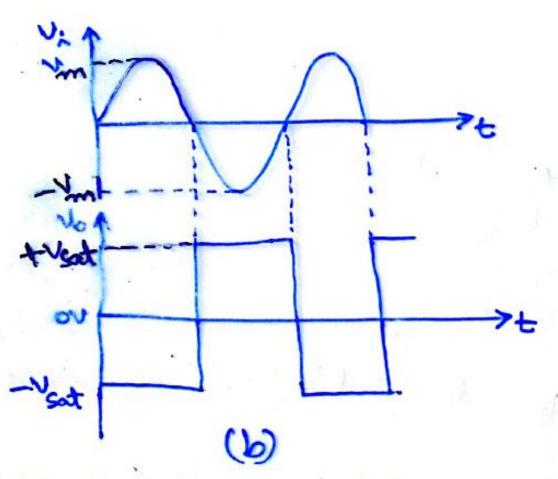

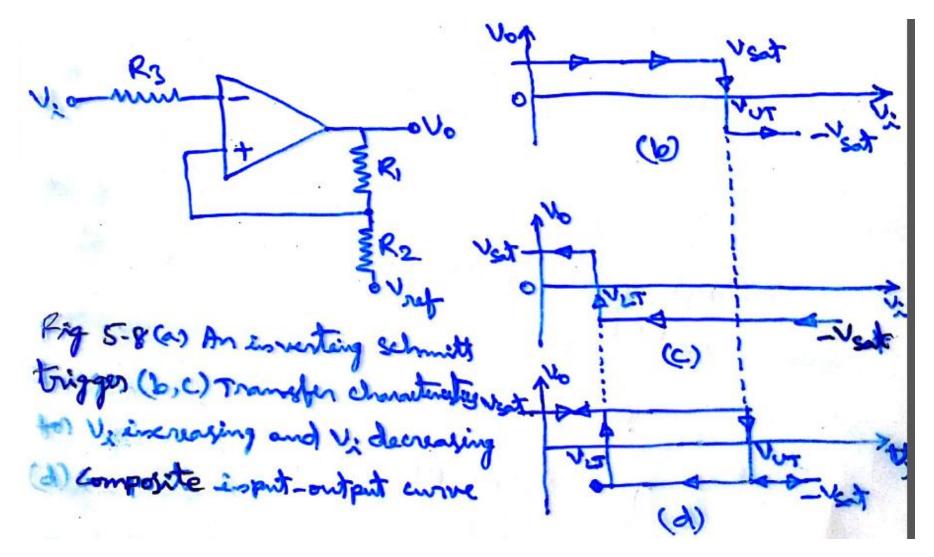

- Figure 5.8 (a) shows a regenerative comparator. The circuit is also known as Schmitt trigger

- The input voltage Vi triggers the output Vo every time it crosses certain voltage levels. These voltage levels are called Upper threshold voltage (Vut) and Lower threshold voltage (Vlt).

- The hysteresis width is the difference between these two threshold voltages ie Vut – Vlt. These threshold voltages are calculated as follows.

- Suppose that the output voltage Vo is +Vsat. The voltage at +ve input terminal will be

- Vref + (R2/(R1+R2)) (Vsat Vref) = Vut

- This voltage is called as Upper threshold voltage Vut

- As long as Vi is less than Vut, the output Vo remains constant at +Vsat. When Vi is just greater than Vut, the output regeneratively switches to – Vsat and remains at this level as long as Vi > Vut as shown in Figure 5.8 (b).

- For Vo = -Vsat, the voltage at +ve input terminal is

Vref + (R2/R1+R2) (-Vsat Vref) = Vlt

Vref (R2/R1+R2) (Vsat + Vref) = Vlt

this voltage is referred to as lower threshold voltage Vlt

- The input voltage Vi must become lesser than Vlt in order to cause Vo to switch from –Vsat to +Vsat. A regenerative transition takes place as shown in Figure 5.8(c) and the output Vo returns from –Vsat to +Vsat almost instantaneously.

- The complete transfer characteristics are shown in Figure 5.8 (d).

- Note that Vlt < Vut and the difference between these two voltages is the hysteresis width Vh and can be written as

Vh = Vut - Vlt = 2R2 Vsat/(R1+R2)

- The resistor R3 in figure 5.8(a) is chosen equal to R1||R2 to compensate for the input bias current.

- A non-inverting Schmitt trigger is obtained if Vi and Vref are interchanged in figure 5.8(a).

# Voltage Regulators

- A voltage regulator is a circuit that supplies constant voltage regardless of changes in load currents

- Although voltage regulators can be designed using opamps, it is quicker and easier to use IC voltage regulators.

- Furthermore, IC voltage regulators are versatile and relatively inexpensive and are available with features such as programmable output, current/voltage boosting, internal short-circuit current limiting, thermal shutdown and floating operation for high voltage applications.

# Voltage Regulators cntd..

- IC voltage regulator are of the following types

- Fixed output voltage regulators: +ve and/or –ve output voltage

- Adjustable output voltage regulators: +ve or –ve output voltage

- Switching regulators

- Special regulators

- Except for the switching regulators, all other types of regulators are called LINEAR regulators.

- The impedance of a linear regulator's active element may be continuously varied to supply a desired current to the load.

- On the other hand, in the switching regulator a switch is turned on and off at a rate such that the regulator delivers the desired average current in periodic pulses to the load.

# Voltage Regulators cntd..

- Because the switching element dissipates negligible power in either the ON or OFF state, the switching regulator is more efficient than the linear regulator.

- Nevertheless, in switching regulators the power dissipation is substantial during the switching intervals (ON to OFF or OFF to ON). In addition, most loads can not accept the average current in periodic pulses. Therefore, most practical regulators are of the linear type.

# Voltage Regulators cntd..

- Voltage regulators are commonly used for laboratory-type power supplies.

- Almost all power supplies use some type of voltage regulator IC because voltage regulators are simple to use, reliable, low in cost, and, above all, available in a variety of voltage and current ratings.

## Performance Parameters

There are four typical performance parameters for voltage regulators. They are LINE regulation, LOAD regulation, temperature stability and ripple rejection.

• LINE or INPUT regulation: it is defined as the change in output voltage for a change in the input voltage and is usually expressed in milli volts or as a percentage of output voltage Vo.

### Performance Parameters cntd..

- LOAD Regulation: It is the change in output voltage for a change in load current and is also expressed in milli volts or as a percentage of Vo

- Temperature stability: It is the change in output voltage per unit change in the temperature and is expressed in either milli volts/°C or parts per million (ppm)/°C

### Performance Parameters cntd..

- Ripple Rejection: it is the measure of a regulator's ability to reject ripple voltages. It is usually expressed in decibels.

- The smaller the values of line regulation, load regulation and the temperature stability, the better the regulator.

- Dropout Voltage: It is the difference between input and output voltages.

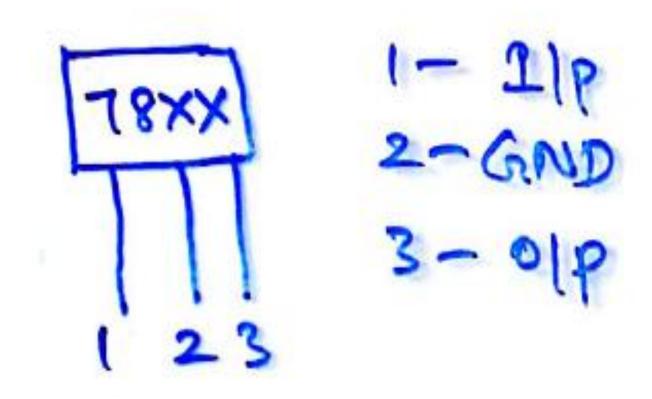

# Types of Voltage Regulators

- Fixed Output Voltage Regulators:

- Positive Output voltage regulator series:

| Device Type | O/P Voltage<br>(Volts) | Max .Input Voltage<br>(Volts) |

|-------------|------------------------|-------------------------------|

| 7805        | 5.0                    | 35                            |

| 7806        | 6.0                    | 35                            |

| 7808        | 8.0                    | 35                            |

| 7812        | 12.0                   | 35                            |

| 7815        | 15.0                   | 35                            |

| 7818        | 18.0                   | 35                            |

| 7824        | 24.0                   | 40                            |

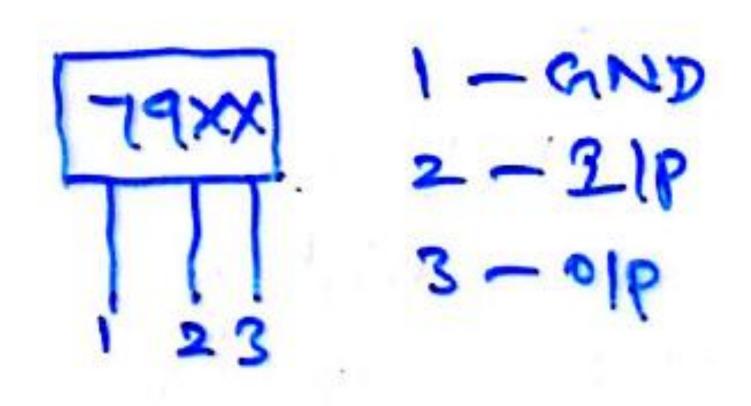

### Negative Output voltage regulator series:

| Device Type | O/P Voltage<br>(Volts) | Max .Input Voltage<br>(Volts) |

|-------------|------------------------|-------------------------------|

| 7902        | -2.0                   | -35                           |

| 7905        | -5.0                   | -35                           |

| 7905.2      | -5.2                   | -35                           |

| 7906        | -6.0                   | -35                           |

| 7908        | -8.0                   | -35                           |

| 7912        | -12.0                  | -35                           |

| 7915        | -15.0                  | -35                           |

| 7918        | -18.0                  | -35                           |

| 7924        | -24.0                  | -40                           |

#### **Adjustable Output Voltage Regulators:**

- In the case of fixed voltage regulators, for each voltage a separate device is to be used. This increases the inventory and hence the cost.

- Therefore, Adjustable voltage regulators came into picture. These regulators provide many voltages ranging from 1.2 to 57 volts.

- In addition, these have more versatility, more performance and more reliability than fixed voltage regulators.

- Adjustable +ve Voltage Regulators LM317 and Adjustable –ve Voltage Regulators – LM337

#### **Switching Regulators:**

- Switching regulators are called so because these use a switch in the circuit.

- Switching regulators come in various circuit configurations including the Fly-back, Feed-forward, Push-pull, and non-isolated single-ended or singlepolarity types.

- Switching regulators can operate in any of three modes: Step-up, step-down or polarity inverting.

- Switching regulator is often referred to as a DC transformer.

- Eg: IC μA78S40 from Fairchild.

### **Special Regulators:**

- It is used as

- Voltage References: It is used as a reference voltage in A/D and D/A converters

- Voltage Inverter: It is used in Data Acquisition and Microprocessor-based systems in which a +ve supply is available and an additional –ve supply is required.

# IC 723 Regulator and It's Features

- 3 terminal voltage regulators are capable of producing only fixed +ve or –ve output voltages. Moreover, such regulators do not have short circuit protection.

- Therefore these 3 terminal regulators evolved into dual polarity variable voltage regulators and further evolved into the monolithic linear voltage regulators and monolithic switching regulators.

- One example for monolithic linear voltage regulator is IC723.

- IC723 general purpose regulator overcomes the limitations of 3 terminal fixed voltage regulators

- IC723 is a low current device.

- 150 mA o/p current without external pass transistor.

- o/p currents in excess of 10A possible by adding external transistors

- Input voltage 40 V maximum.

- O/p voltage adjustable from 2V to 37 V.

- Can be used as either a linear or a switching regulator.

Limitations: it has no built-in thermal protection.

End of Unit I

### Unit II

Op-Amp, IC-555 & IC 565 Applications

### Introduction to Filters

- Based on the components used in the circuit the filters are divided into following categories.

- Active filters

- Passive filters

#### **Active Filters:**

Active filters employ transistors or op-amps in addition to resistors and capacitors.

#### **Passive Filters:**

Here the type of element used dictates the operating frequency range of the filter.

#### Eg:

- RC filters are used for audio or low frequency operation.

- LC or Crystal filters are used at RF or High frequencies.

- An active filter offers the following advantages over a Passive filter.

- Gain and Frequency adjustment flexibility: Since the op-amp is capable of providing a gain, the input signal is not attenuated as it is in a passive filter. In addition, the active filter is easier to tune or adjust.

- No Loading problem: Because of the high input resistance and low output resistance of the op-amp, the active filter does not cause loading of the source or load.

- Cost: Typically, active filters are more economical than passive filters. This is because of the variety of cheaper op-amps and the absence of the inductors.

- Although active filters are most extensively used in the field of Communications and Signal processing, they are employed in one form or another in almost all sophisticated electronic systems.

- The different systems that use Active filters are Radio, television, telephone, Radar, Space satellites, and bio-medical equipment.

- Based on the operating frequency the filters are classified as follows.

- Low pass filter

- High pass filter

- Band pass filter

- Band stop filter

- All pass filter

- Each of these filters uses an op-amp as an active element and resistors and capacitors as passive elements.

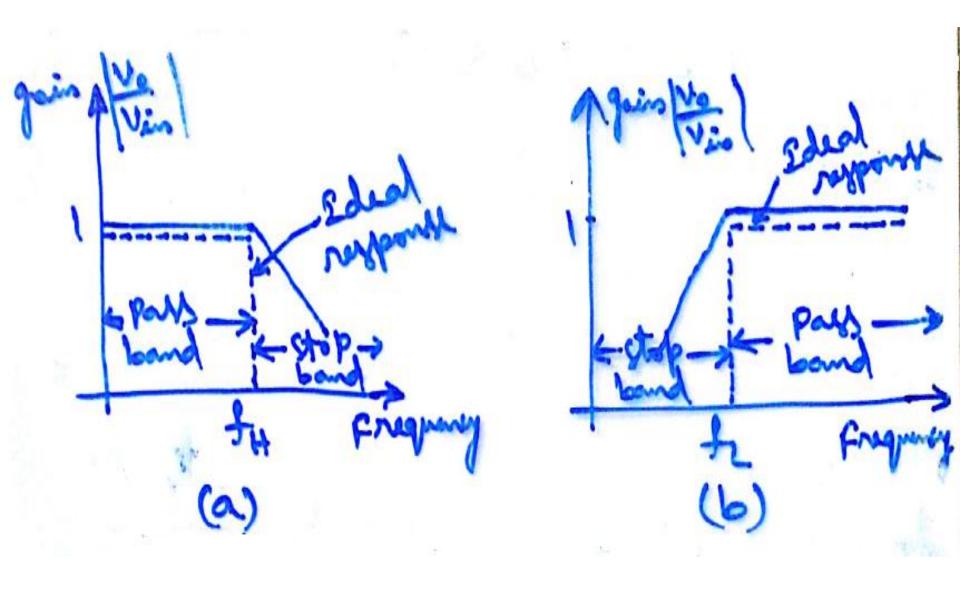

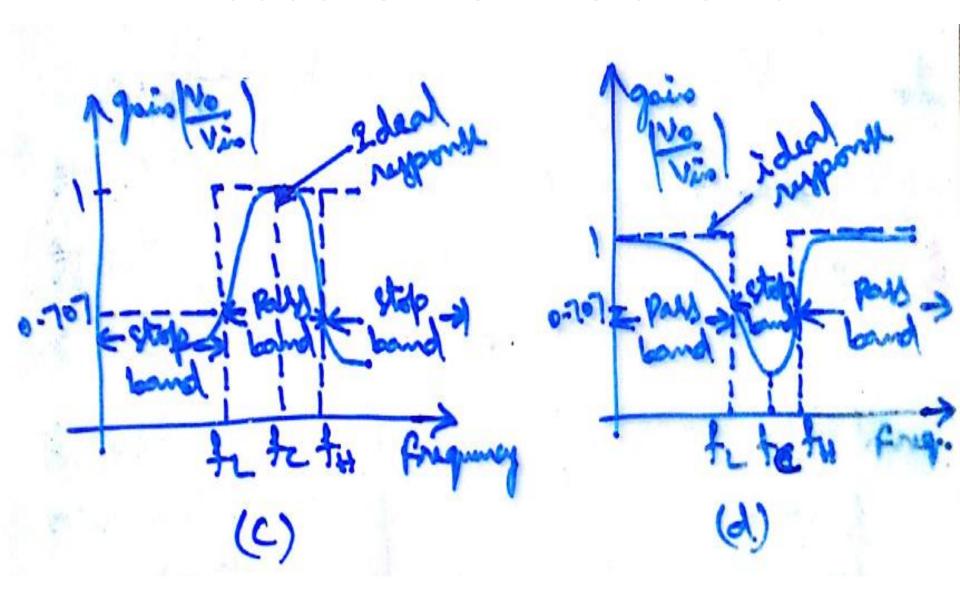

- Figure 8.1 shows the frequency response characteristics of the five types of filters.

- Figure 8-1(a) shows the frequency response of low pass filter. As indicated by dashed line, an ideal filter has a zero loss in its pass band and infinite loss in its stop band

- Unfortunately, ideal filter response is not practical.

However, it is possible to obtain a practical response

that approximates the ideal filter response by using

special design techniques as well as precision

component values and high speed op-amps.

- Butterworth, chebyshev and caver filters are some of the most commonly used practical filters that approximate the ideal response.

- The key characteristics of Butterworth filters is that it has a flat pass band as well as stop band.

For this reason, it is sometimes called a flat-flat filter.

- Figure 8-1(b) shows a high pass filter with a stop band 0 < f < fL and pass band f >fL.

- A band pass filter has a pass band between two cut-off frequencies fH and fL, where fH >fL and two stop bands 0<f<fL and f>fH.

Band width of the band pass filter – fH-fL.

- The band reject filter performs exactly opposite to the band pass, ie it has a band stop between two cut off frequencies fH and fL and two pass bands 0<f<fL and f>fH.

- The band reject filter is also called as band stop or band elimination filter

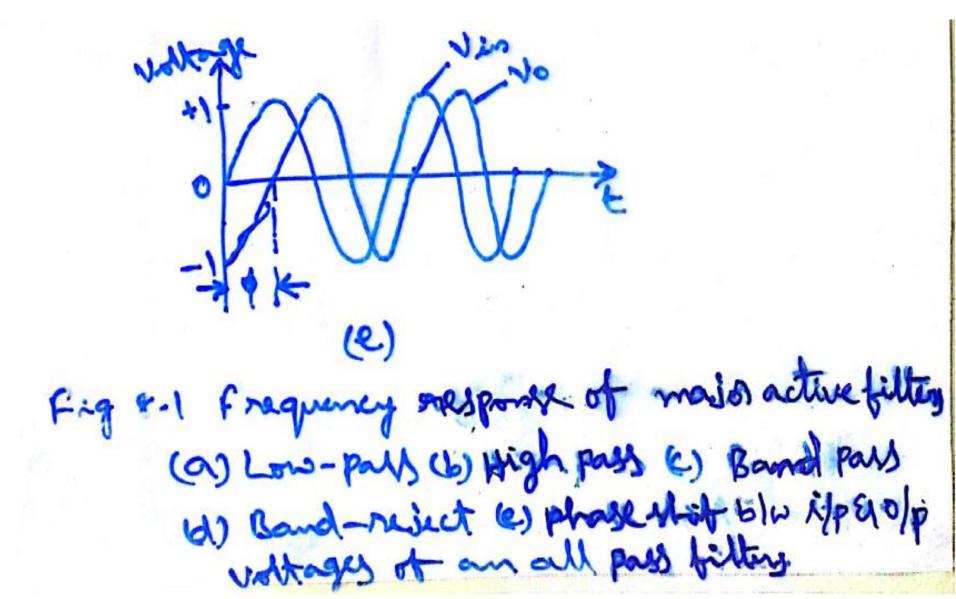

- Figure 8-1(e) shows the phase shift between input and output voltages of an all pass filter. This filter passes all frequencies equally well ie input and output voltages are equal in amplitude for all frequencies, with the phase shift between the two a function of frequency.

- As shown figure 8-1 (a) (d), the actual response curves of the filters in the stop band either steadily decrease or increase or both with increase in frequency.

- The rate at which the gain of the filter changes in the stop band is determined by the order of the filter.

- For first order low pass filter, gain decreases by 20 dB/decade in the stop band.

- For second order low pass filter, gain decreases by 40 dB/decade in the stop band.

- By contrast, for first order high pass filter, gain increases by 20 dB/decade in the stop band.

- For second order high pass filter, gain increases by 40 dB/decade.

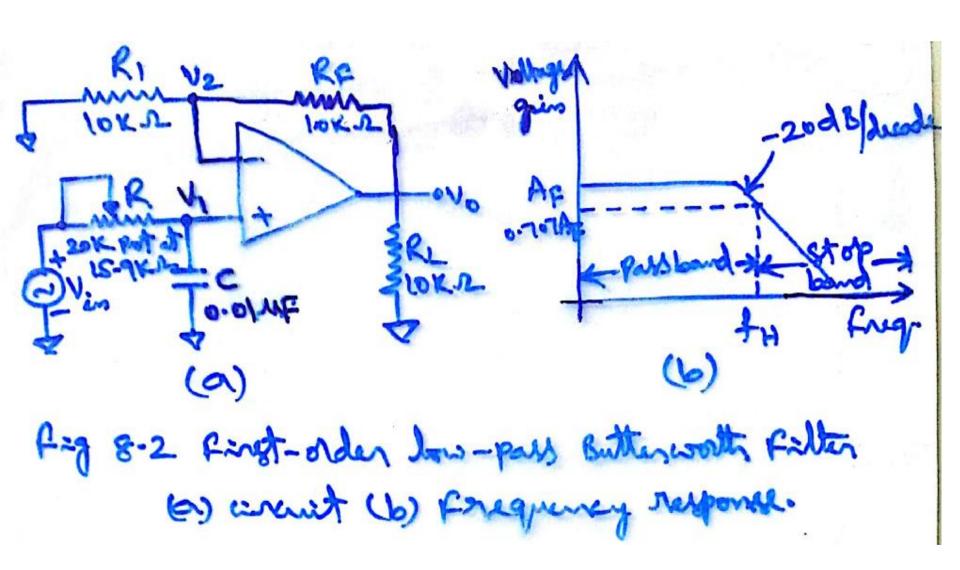

#### First Order Low pass Butterworth filter

Figure 8-2 shows a first order low pass Butter worth filter that uses an RC network for filtering. Note that the op-amp is used in the non-inverting configuration, hence it does not load down the RC network. Resistors R1 and Rf determine the gain of the filter.

According to the voltage divider rule, the voltage at the non-inverting terminal (across capacitor C) is

```

V1 = -jXc/(R-jXc) \ Vin \quad ------ eq(1)  where \ j=\sqrt{-1} \ and \ -jXc = 1/j2\Pi fC  simplifying \ eq(1), \ we \ get  V1 = Vin \ / \ 1+ \ j2\Pi fRC  Output \ voltage \ Vo= (1+(Rf/R1)) \ V1  ie \ Vo = (1+(Rf/R1)) \ (Vin/(1+j2\Pi fRC))

```

Vo/Vin = Af/(1+j (f/fH)) ----- eq(2)

where Vo/Vin = gain of the filter as a function of frequency.

Af= 1+ (Rf/R1) = pass band gain of the filter

f = frequency of the input signal

$fH = 1/2\Pi RC = high cutoff frequency of the filter.$

The gain magnitude and phase angle equations of the low pass filter can be obtained by converting eq(2) into it's equivalent polar form, as follows.

|Vo/Vin| = Af/

$$\sqrt{(1+(f/fH)^2)}$$

----- eq(3)

$\phi$  = - tan^-1(f/fH)

Where  $\phi$  is the phase angle in degrees

The operation of the low pass filter can be verified from the gain magnitude equation (3).

- At very low frequencies, that is, f<fH |Vo/Vin| = Af

- At f = fH, |Vo/Vin| = 0.707 Af

- At f>fH, |Vo/Vin| < Af</li>

- Thus the low pass filter has a constant gain Af from 0 Hz to the almost high cutoff frequency fH

- At fH, the gain is 0.707 Af, and after fH it decreases at a constant rate with as increase in frequency [see fig 8-2 b]

- The frequency f =fH is called the cutoff frequency because the gain of the filter at this frequency is down by 3 dB from 0 Hz.

- Other equivalent terms for cut off frequency are -3dB frequency, break frequency or corner frequency.

#### Filter Design

A low pass filter can be designed by implementing the following steps

- 1 Choose a value of high cut off frequency fH

- 2 Select a value of C less than or equal to 1  $\mu$ F

- (Mylar or tantalum capacitors are recommended for better performance)

- 3 Calculate the value of R using R =  $1/2\pi$  fH C

- 4 Finally, select values of R1 anf Rf dependant on the desired pass band gain Af using

$$Af = 1 + (Rf/R1)$$

**Example 1:** Design a low pass filter at a cut off frequency of 1 KHz with a pass band gain of 2

#### **Solution:**

Follow the preceding design steps

- 1 fH = 1 KHz

- 2 Let C =  $0.01 \mu F$

- 3 Then R = 1/2 Π (10<sup>3</sup>) (10<sup>-8</sup>) = 15.9 KΩ (use a 20 KΩ pot.)

- 4 Since the pass band gain is 2, R1 and Rf must be equal. Therefore, let R1 = Rf = 10 K $\Omega$

- The complete circuit with components values is shown in Fig 8-2 a.

#### **Frequency Scaling**

- Once a filter is designed there may sometimes be a need to change its cut off frequency. The procedure used to convert an original cut off frequency fH to a new cut off frequency fH1 is called frequency scaling.

- Frequency scaling is accomplished as follows

- To change a high cut off frequency, multiply R or C but not both, by the ratio of original cut off frequency to new cut off frequency.

#### **Example 2:**

Using the frequency scaling technique, convert 1 KHz cut off frequency of the low pass filter of Example 1 to a cut off frequency of 1.6 KHz

**Solution:** To change a cut off frequency from 1 KHz to 1.6 KHz, we multiply the 15.9 K $\Omega$  resistor by Original cut off frequency/new cut off frequency = 1 KHz/1.6 KHz = 0.625

Therefore, new resistor R = 15.9 K $\Omega$  \* 0.625 = 9.94 K $\Omega$  However, 9.94 K $\Omega$  is not a standard value.

Therefore, use R=  $10K\Omega$  potentiometer and adjust it to  $9.94~K\Omega$ .

Thus the new cut off frequency is

fH1 = 1/2Π (0.01 μF) (9.94 KΩ) = 1.6 KHz.

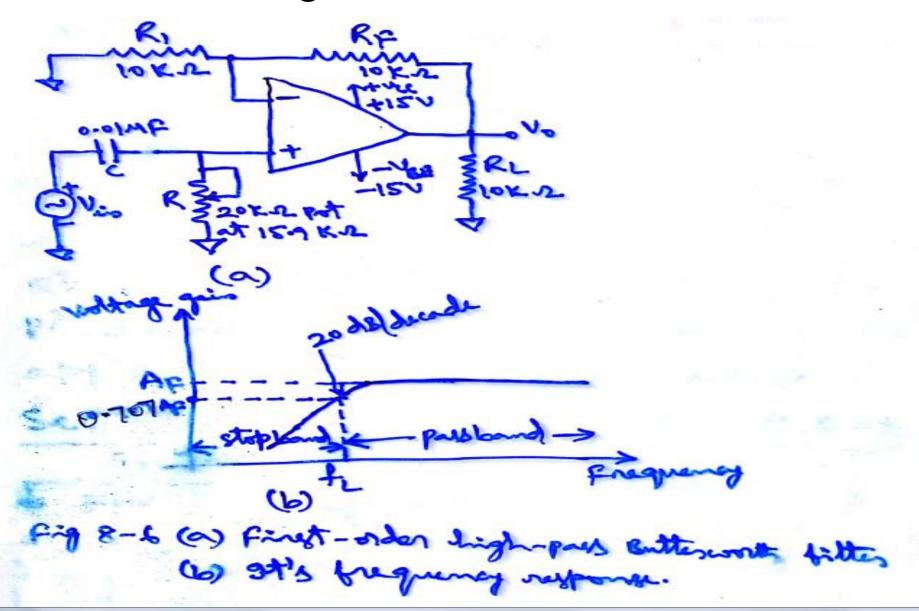

### First Order High Pass Butterworth filter

- High pass filters are often formed simply by interchanging the frequency-determining resistors and capacitors in low pass filters.

- That is, a first order high pass filter is formed from a first order low pass type by interchanging components R & C.

- Figure 8.6 shows a first order high pass Butter worth filter with a low cut off frequency of fL.

This is the frequency at which the magnitude of the gain is 0.707 times its pass band value.

- Obviously all frequencies higher than fL are pass band frequencies, with the highest frequency determined by the closed loop band width of the op-amp.

- For the first order high pass filter of Figure 8.6a, the output voltage is

```

Vo = (1+(Rf/R1)) (j2\Pi fRC/(1+j2\Pi fRC)) Vin Vo/Vin = Af[j(f/fL)/(1+j(f/fL)) where Af = 1+(Rf/R1), & fL = 1/2\Pi RC Hence the magnitude of the voltage gain is |Vo/Vin| = Af (f/fL)/\sqrt{(1+(f/fL)^2)}

```

Since the high pass filters are formed from low pass filters simply by interchanging Rs and Cs, the design and frequency scaling procedures of the low pass filters are also applicable to high pass filters.

### Wave form Generators

- There are different types of wave form generators which are given below.

- 1 Square wave generator

- 2 Triangular wave generator

- 3 Saw tooth wave generator

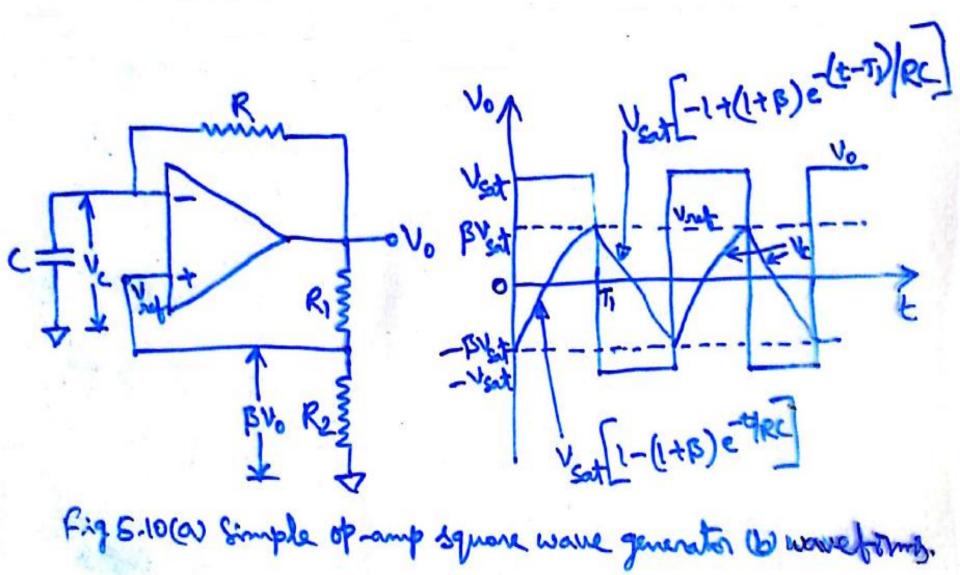

#### **Square wave Generator (Astable Multivibrator)**

A simple op-amp square wave generator is shown in Figure 5.10a.

# Square wave generator

- It is also called a Free running oscillator.

- The principle of generation of square wave output is to force an op-amp to operate in saturation region.

- In Figure 5.10(a), fraction  $\beta = R2/(R1+R2)$  of the output is fed back to the +ve input terminal. Thus the reference voltage Vref is  $\beta$ Vo and may take values as + $\beta$ Vsat or – $\beta$ Vsat.

- The output is also fed back to the –ve input terminal after integrating by means of a low pass RC combination.

- Whenever input at the –ve input terminal just exceeds Vref, switching takes place resulting in a square wave output.

- In Astable multivibrator, both the states are quasi stable.

#### **Frequency Derivation**

The frequency is determined by the time it takes the capacitor to charge from  $-\beta Vsat$  to  $+\beta Vsat$  and vice versa.

The voltage across the capacitor as a function of time is given by

$$Vc(t) = Vf + (Vi - Vf) e^{-t}/RC$$

where, the final value, Vf = +Vsat

and the initial value,  $Vi = -\beta Vsat$

Therefore  $Vc(t) = +Vsat + (-\beta Vsat - Vsat) e^{-t}/RC$

$$Vc(t) = Vsat - Vsat(1+\beta) e^{-t}/RC$$

At t = T1, voltage across the capacitor reaches  $\beta V$ sat and switching takes place.

Therefore

$$Vc(T1) = \beta Vsat = Vsat - Vsat(1 + \beta) e^{-T1/RC}$$

After algebraic manipulation, we get

This gives only one half of the period.

Therefore the total time period,  $=2*T1 = 2RC \ln (1+\beta)/(1-\beta)$  and the output waveform is symmetrical.

If R1 = R2, then  $\beta$  = 0.5 and T = 2RC ln 3 and for R1=1.16 R2, it can be seen that T = 2RC or fo = 1/2RC

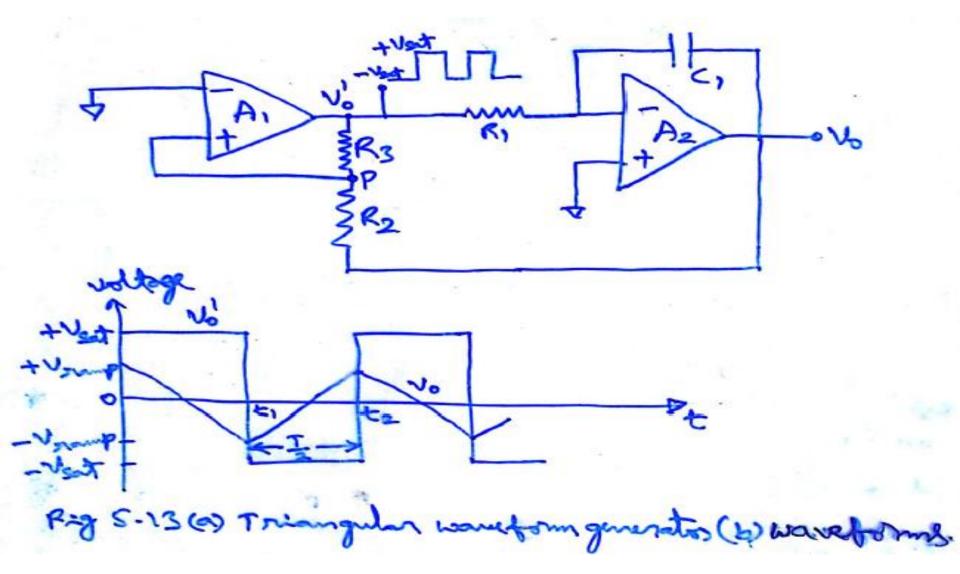

# Triangular Wave Generator

- It basically consists of a two level comparator followed by an integrator.

- The output of the comparator A1 is a square wave of amplitude + or Vsat and is applied to the –ve input terminal of the integrator A2 producing a triangular wave. This triangular wave is fed back as input to the comparator A1 through a voltage divider R2R3.

- Initially, let us consider that the output of the comparator A1 is at +Vsat. The output of the integrator A2 will be a –ve going ramp as shown in figure 5.13b. This one end of the voltage divider R2R3 is at a voltage +Vsat and the other at the –ve going ramp of A2.

- At a time t=t1, when the –ve going ramp attains a value of –Vramp, the effective voltage at point p becomes slightly less than 0 volts. This switches the output of A1, from positive saturation level to negative saturation level – Vsat.

- During the time when the output of A1 is at -Vsat, the output of A2 increases in the positive direction.

- And at the instant t=t2, the voltage at point p becomes just above 0 volts, thereby switching the output of A1 from –Vsat to +Vsat. The cycle repeats and generates a triangular waveform.

- It can be seen that the frequency of the square wave and triangular wave will be the same.

- However, the amplitude of the triangular wave depends upon the RC value of the integrator A2 and output voltage level of A1.

#### **Derivation of Frequency of Triangular Waveform**

The effective voltage at point p during the time when output of A1 is at +Vsat level is given by

-Vramp+(R2/(R2+R3)) [+Vsat - (-Vramp)] -- Eq(1)

At t=t1, the voltage at point p becomes approximately equal to zero. Therefore from Eq(1), we get -Vramp = (-R2/R3) (+Vsat)

Similarly at t=t2, when the output of A1 switches from –Vsat to +Vsat

Vramp = (-R2/R3) (-Vsat) = (R2/R3) Vsat

Therefore peak to peak amplitude of the triangular wave is

$$Vo(pp) = +Vramp - (-Vramp)$$

Vo (pp) =

$$2 \text{ Vramp} = 2 (R2/R3) \text{ Vsat} ---- Eq(2)$$

The output switches from –Vramp to +Vramp in half the time period T/2.

Putting the values in the basic integrator equation Vo = -(1/RC) Vi dt, we get

Vo(pp)=-(1/R1C1) O T/2 (-Vsat)dt = (Vsat/R1C1) (T/2)

Therefore T=2 R1C1 Vo(pp)/Vsat

Putting the value of Vo(pp) from Eq(2), we get

Hence the frequency of oscillation fo is fo = 1/T = R3/4 R1 C1 R2

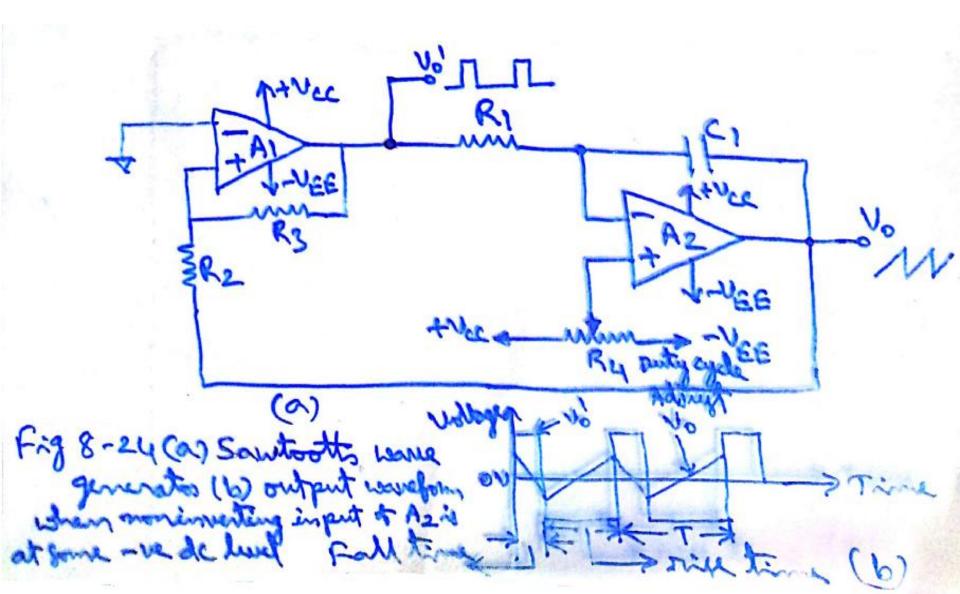

#### Sawtooth Wave Generator

- The difference between the triangular and sawtooth waveforms is that

- rise time and fall time are equal Triangular rise time and fall time are unequal Sawtooth

- The triangular wave generator can be converted into a sawtooth wave generator by injecting a variable DC voltage into the non-inverting terminal of the integrator A2.

- This can be accomplished by using the potentiometer and connecting it to the +Vcc and -Vee as shown in Figure 8-24(a)

### Sawtooth Wave Generator cntd..

### Sawtooth Wave Generator cntd...

- Depending on the R4 setting, a certain DC level is inserted in the output of A2.

- Now suppose that the output of A1 is a square wave and the potentiometer R4 is adjusted for a certain DC level.

- This means that the output of A2 will be a triangular wave, riding on some DC level that is a function of the R4 setting.

- The duty cycle of the square wave will be determined by the polarity and amplitude of this DC level.

- A duty cycle less than 50% will then cause the output of A2 to be a sawtooth.

### Sawtooth Wave Generator cntd...

With the wiper at the center of R4, the output of A2 is a triangular wave. For any other position of R4 wiper, the output is a sawtooth waveform.

R4 wiper is towards –Vee, the rise time is more

R4 wiper is towards +Vcc, the fall time is more

### Introduction to IC 555 Timer

- The 555 timer is a highly stable device for generating accurate time delay or oscillation.

- Signetics corporation first introduced this device as the SE555/NE555 and it is available in two package styles, 8 pin circular type, To-99 can or 8-pin mini DIP or as 14-pin DIP.

- A single 555 timer can provide time delay ranging from µsec to hours.

- The 555 timer can be used with supply voltage in the range of +5 Volts to +18 volts and can drive load upto 200mA.

- It is compatible with both TTL and CMOS logics.

### Introduction to IC 555 Timer cntd...

- Because of wide range of supply voltage, the 555 timer is versatile & easy to use in various applications.

- Various applications include oscillators, pulse generator, ramp & square wave generator, mono shot multivibrator, burglar alarm, traffic light control and voltage monitor etc.

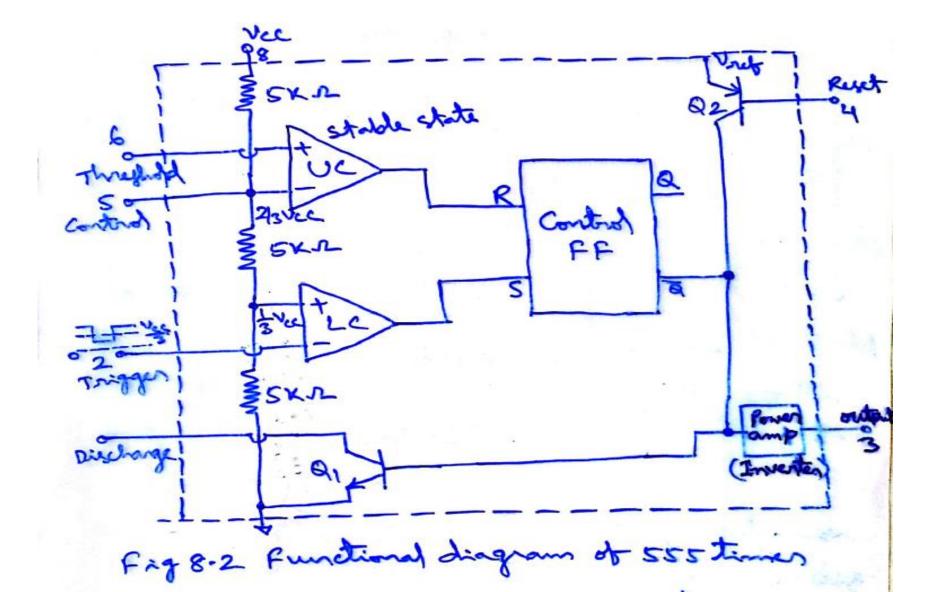

#### **Functional Diagram of 555 Timer**

Figure 8.2 gives the functional diagram for 555 IC timer.

# Functional Diagram of 555 Timer

### Functional Diagram of 555 Timer cntd...

- Referring to Figure 8.2, 3  $5K\Omega$  internal resistors act as voltage divider, providing bias voltage of 2/3 Vcc to the upper comparator (UC), and 1/3 Vcc to the lower comparator (LC) where Vcc is the supply voltage.

- In the stand by(stable) state, the output Q of control filp-flop(FF) is high.

- This makes the output LOW because of power amplifier which behaves like inverter.

- A –ve going trigger pulse is applied to pin 2 and should have its DC level greater than the threshold level of the lower comparator (that is Vcc/3).

### Functional Diagram of 555 Timer cntd...

- At the –ve going edge of the trigger, as the trigger passes through Vcc/3, the output of the lower comparator goes HIGH and sets the FF.

- During the positive excursion, when the threshold voltage at pin 6 passes through 2/3 Vcc, the output of the upper comparator goes HIGH and resets the  $FF(Q=0, \overline{Q}=1)$ .

- The reset input (pin 4) provide a mechanism to reset the FF in a manner which over rides the effect of any instruction coming to FF from lower comparator.

- When this reset is not used, it is returned to Vcc

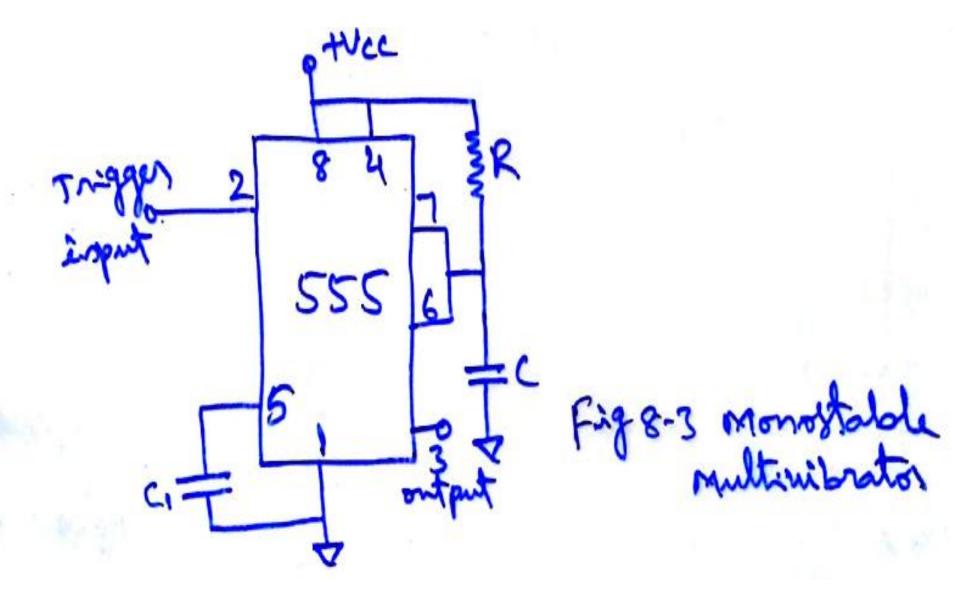

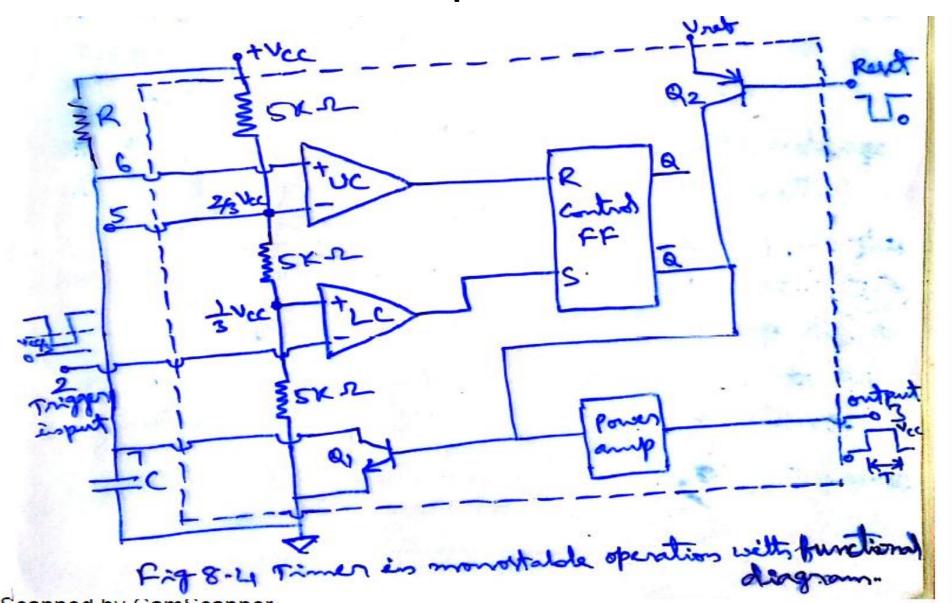

## Monostable Operation

Figure 8.3 shows a 555 timer connected for mono stable operation and its functional diagram is shown in Figure 8.4

## Monostable Operation cntd..

# Monostable Operation cntd..

## Monostable Operation cntd..

- In the stand by state, FF holds transistor Q1 on, thus clamping the external timing capacitor C to ground. The output remains at ground potential ie low.

- As the trigger passes through Vcc/3, the FF is set ie Q = 0. This makes the transistor Q1 off and the short circuit across the timing capacitor C is released. As Q is low, output goes HIGH (= Vcc).

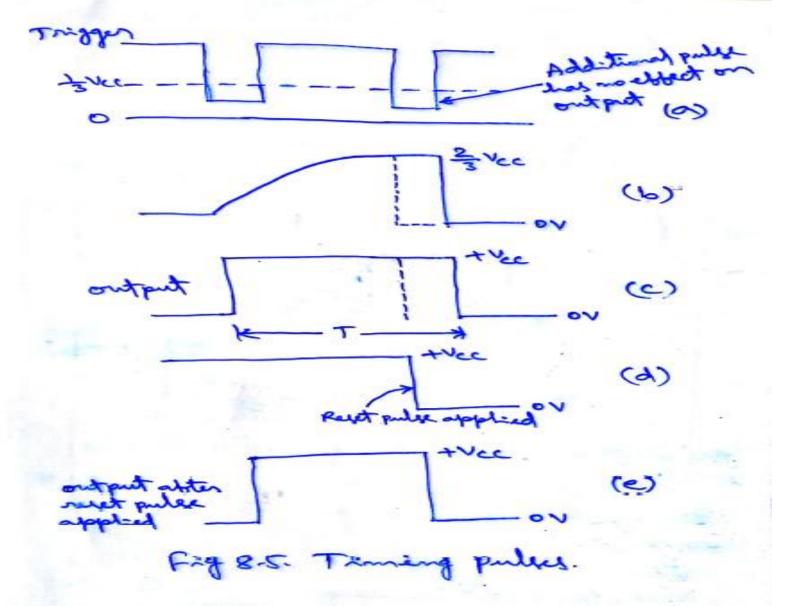

- Since C is unclamped, voltage across it rises exponentially through R towards Vcc with a time constant RC as in Figure 8.5 b.

#### Monostable Operation cntd...

- After a time period T the capacitor voltage is just greater than 2/3 Vcc and the upper comparator resets the FF, that is, R =1, S=0. This makes Q = 1, transistor Q1 goes on (ie saturates), thereby discharging the capacitor C rapidly to ground potential. The output returns to the ground potential as shown in Figure 8.5c.

- The voltage across the capacitor as in Figure 8.5b is given by Vc = Vcc(1- e^-t/RC)

At

$$t = T$$

,  $Vc = 2/3 Vcc$

Therefore  $2/3 \text{ Vcc} = \text{Vcc}(1-\text{e}^-\text{T/RC})$

```

e^{-T/RC} = 1 - 2/3 ==> e^{-T/RC} = 3

T/RC = In3 \rightarrow T = 1.1 RC ----- Eq(1)

```

- It is evident from Eq(1) that the timing interval is independent of the supply voltage. It may also be noted that once triggered, the output remains in the HIGH state until time T elapses, which depends only upon R and C. Any additional trigger pulse coming during this time will not change the output state.

- However, if a negative going reset pulse as in Figure 8.5 d is applied to the reset terminal during the timing cycle, transistor Q2 goes off, Q1 becomes on and the external timing capacitor C is immediately discharged. The output now will be as in Figure 8.5 e.

# Applications in Monostable Mode

- Some applications of monostable multivibrator are

- Missing pulse detector

- Linear ramp generator

#### **Missing Pulse Detector:**

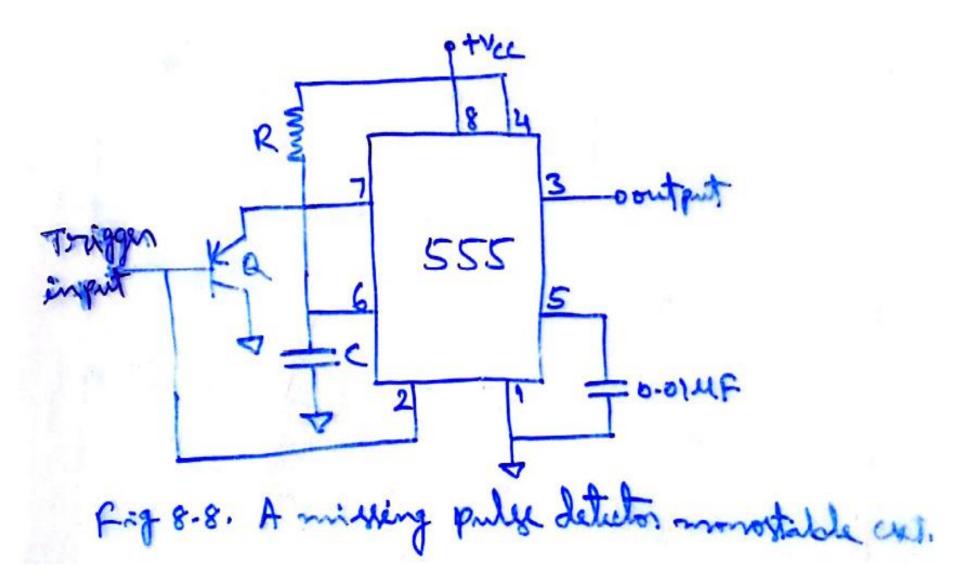

Missing pulse detector circuit using 555 timer is shown in Figure 8.8.

#### Applications in Monostable Mode cntd..

#### Applications in Monostable Mode cntd..

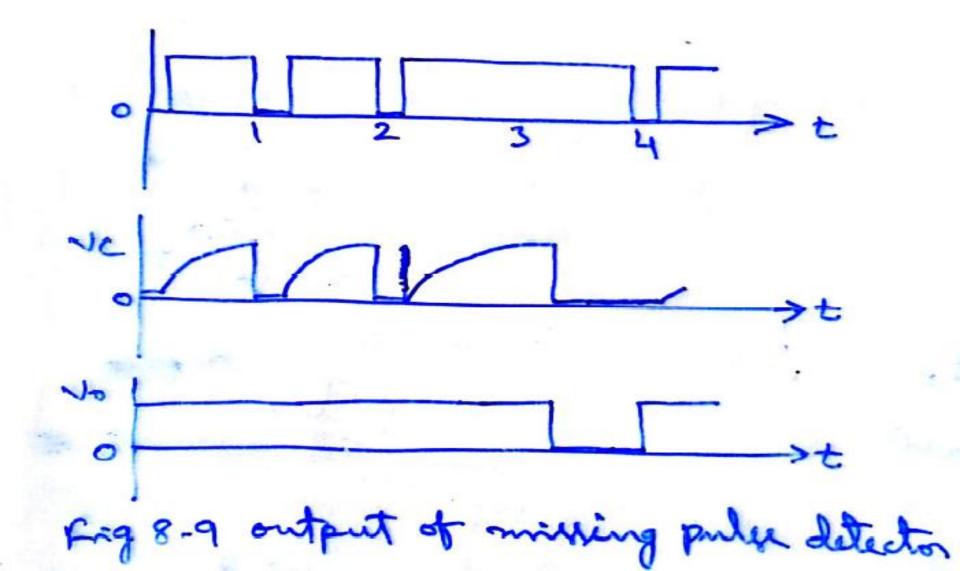

- Whenever, input trigger is low, the emitter diode of the transistor Q is forward biased. The capacitor C gets clamped to few tenths of a volt (~0.7V). The output of the timer goes HIGH.

- So long the trigger pulse train keeps coming at pin 2, the output remains HIGH.

- However, if a pulse misses, the trigger input is high and transistor Q is cutoff. The 555 timer enters into normal state of monostable operation. The output goes LOW after time T of the mono-shot.

- Thus this type of circuit can be used to detect missing heart beat.

#### Applications in Monostable Mode cntd..

## **Astable Operation**

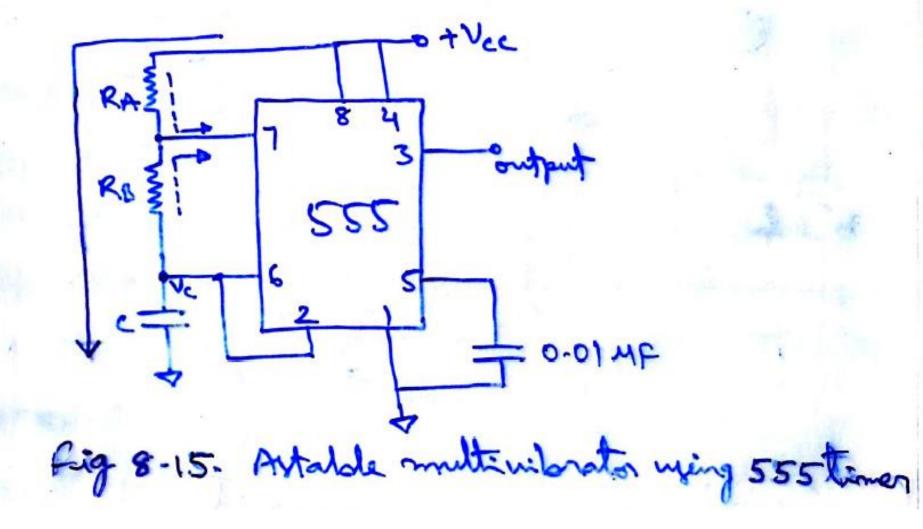

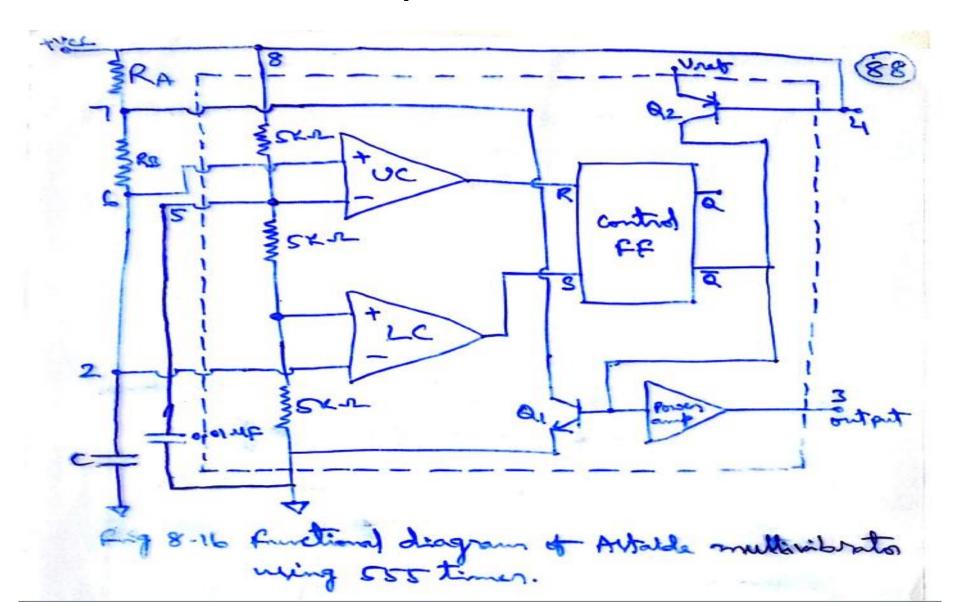

The device is connected for Astable operation as shown in Figure 8.15.

For better understanding the complete diagram of Astable multivibrator with detailed internal diagram of 555 is shown in Figure 8.16.

- Comparing with the monostable operation, the timing resistor is now split into two sections Ra and Rb. Pin 7 of discharging transistor Q1 is connected to the junction of Ra and Rb.

- When the power supply Vcc is connected, the external timing capacitor C charges towards Vcc with a time constant (Ra+Rb)C. During this time, output(pin 3) is HIGH (equals Vcc) as RESET R=0, SET S=1 and this combination makes Q=0 which has unclamped the timing capacitor C.

- When the capacitor voltage equals 2/3 Vcc the upper comparator triggers the control FF so that Q=1. This, in turn, makes the transistor Q1 on and capacitor C starts discharging towards ground through Rb and transistor Q1 with a time constant Rb C.

- Current also flows into transistor Q1 through Ra.

- Resistors Ra and Rb must be large enough to limit this current and prevent damage to the discharge transistor Q1.

- The minimum value of Ra is approximately equal to Vcc/0.2 where 0.2 A is the maximum current through the ON transistor Q1.

- During the discharge of the timing capacitor C, as it reaches Vcc/3, the lower comparator is triggered and at this stage S=1, R=0, which turns Q=0. Now Q=0 unclamps the external timing capacitor C. The capacitor C is thus periodically charged and discharged between 2/3 Vcc and 1/3 Vcc respectively.

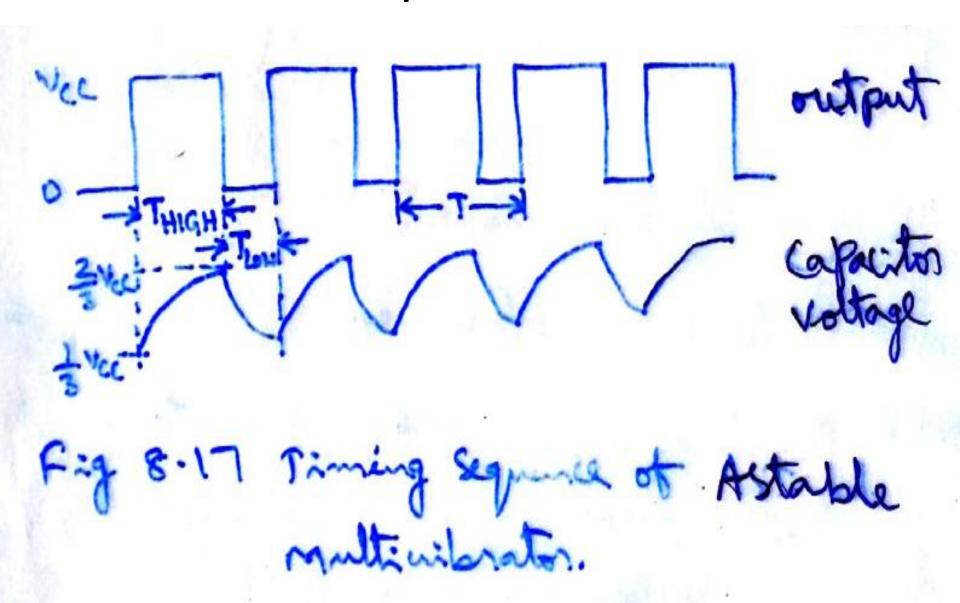

- Figure 8.17 shows the timing sequence and capacitor voltage waveform.

- The length of Time that the output remains HIGH is the time for the capacitor to charge from 1/3 Vcc to 2/3 Vcc. It may be calculated as follows.

- The capacitor voltage for a low pass RC circuit subjected to a step input of Vcc volts is given by Vc = Vcc (1- e^(-t/RC))

- The time t1 taken by the circuit to charge from 0 to 2/3 Vcc is

$$2/3 \text{ Vcc} = \text{Vcc}(1 - e^{-(-t1/RC)}) \rightarrow t1 = 1.09 \text{ RC}$$

And the time t2 to charge from 0 to 1/3 Vcc is 1/3 Vcc = Vcc  $(1-e^{-t2/RC})$   $\rightarrow$  t2 = 0.405 RC So the time to charge from 1/3 Vcc to 2/3 Vcc tHIGH = t1 -t2 = 1.09 RC - 0.405 RC = 0.69 RC So, for the given circuit, tHIGH = 0.69 (Ra+Rb) C

The output is low while the capacitor discharges from 2/3 Vcc to 1/3 Vcc and the voltage across the capacitor is given by

$1/3 \text{ Vcc} = 2/3 \text{ Vcc} e^{-t/RC}$

Solving, we get t =0.69 RC

So for the given circuit, tLOW = 0.69 Rb C

Notice that both Ra & Rb are in the charge path, but only Rb is in the discharge path.

The Duty cycle D of a circuit is defined as the ratio of ON time to the total time period

$$T = tON + tOFF$$

.

In this circuit, when the transistor Q1 is ON, the output goes LOW. Hence

D % =

$$(tLOW / T) * 100$$

=  $Rb/(Ra + 2Rb) * 100$

With the circuit configuration of Fig 8.15 it is not possible to have a duty cycle more than 50% since tHIGH = 0.69 (Ra+Rb) C will always be greater than tLOW = 0.69 Rb C

- In order to obtain a symmetrical square wave ie D

=50%, the resistance Ra must be reduced to zero.

- However, now Pin 7 is connected directly to Vcc and extra current will flow through Q1 when it is ON. This may damage Q1 and hence the timer

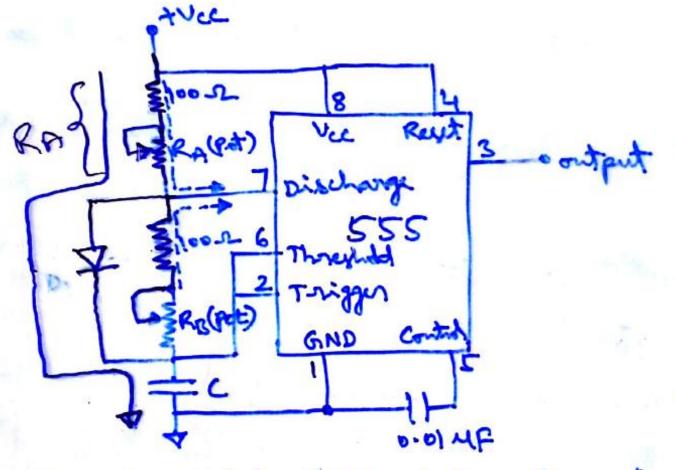

- An alternate circuit which will allow duty cycle to be set at practically any level is shown in Figure 8.19.

Fig 8-19 Adintable duty cycle rectangular

- During the charging portion of the cycle, diode D1 is forward biased effectively short circuiting Rb so that tHIGH = 0.69 Ra C

- However, during the discharging portion of the cycle, transistor Q1 becomes ON, thereby grounding pin 7 and hence the diode D1 is reverse biased. So tLOW = 0.69 Rb C

Therefore T= tHIGH + tLOW = 0.69(Ra+Rb)C

$$\rightarrow$$

f = 1/T = 1.45 /(Ra+Rb)C

And Duty cycle, D = Rb /(Ra+Rb)

Resistors Ra and Rb could be made variable to allow adjustment of frequency and pulse width.

- However, a series resistor of at least 100Ω should be added to each Ra and Rb. This will limit peak current to the discharge transistor Q1 when the variable resistors are at minimum value.

- And, if Ra is made equal to Rb, then 50% duty cycle is achieved.

**Example:** Refer Figure 8.15. For Ra = 6.8 K $\Omega$ , Rb = 3.3 K $\Omega$  and C=0.1  $\mu$ F, calculate (a) tHIGH (b) tLOW (c) free running frequency (d) duty cycle D.

#### **Solution:**

```

a) tHIGH = 0.69(Ra+Rb) C = 0.69 (6.8 K\Omega + 3.3 K\Omega) 0.1 \muF = 0.7 ms b) tLOW = 0.69 Rb C = 0.69 (3.3K\Omega) 0.1 \muF = 0.23 ms

```

```

c) f = 1.45/((Ra +2Rb) C)

= 1.45/((6.8 K\Omega + 2(3.3 K\Omega)) (0.1 \muF))

= 1.07 KHz

d) Duty Cycle D = tLOW / T = Rb/(Ra + 2Rb)

= 3.3 K\Omega /(6.8 K\Omega + 2 (3.3 K\Omega))

= 0.25 = 25%

```

## Applications in Astable Mode

- A couple of applications in Astable mode are

- Pulse position modulator

- FSK Generator

#### **Pulse Position Modulator:**

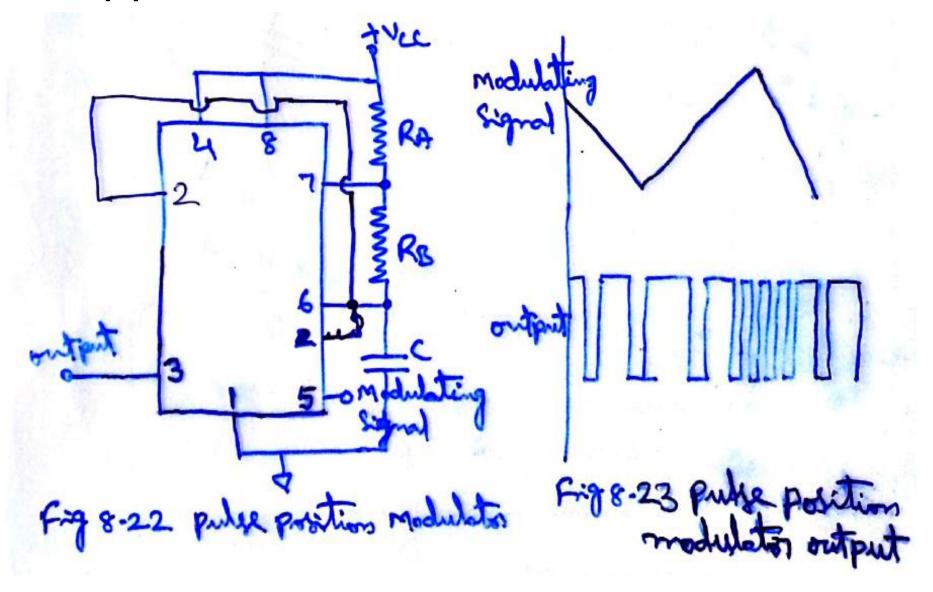

The Pulse Position Modulator can be constructed by applying a modulating signal to pin5 of a 555 timer connected for Astable operation as shown in Figure 8.22.

## Applications in Astable Mode cntd..

#### Applications in Astable Mode cntd..

- The output pulse position varies with the modulating signal, since the threshold voltage and hence the time delay is varied.

- Figure 8.23 shows the output waveform generated for a triangle wave modulation signal. It may be noted from the output waveform that the frequency is varying leading to pulse position modulation.

# Phase Locked Loops: Introduction

- Although the evolution of the phase-locked loop began in the early 1930's, its cost outweighed it's advantages at first.

- With the rapid development of integrated circuit technology, however, the phase locked loop has emerged as one of the fundamental building blocks in electronics technology.

- The phase-locked loop principle has been used in applications such as FM stereo decoders, motor speed controls, tracking filters, frequency synthesized transmitters and receivers, FM demodulators, FSK decoders, and a generation of local oscillator frequencies and in TV and FM tuners.

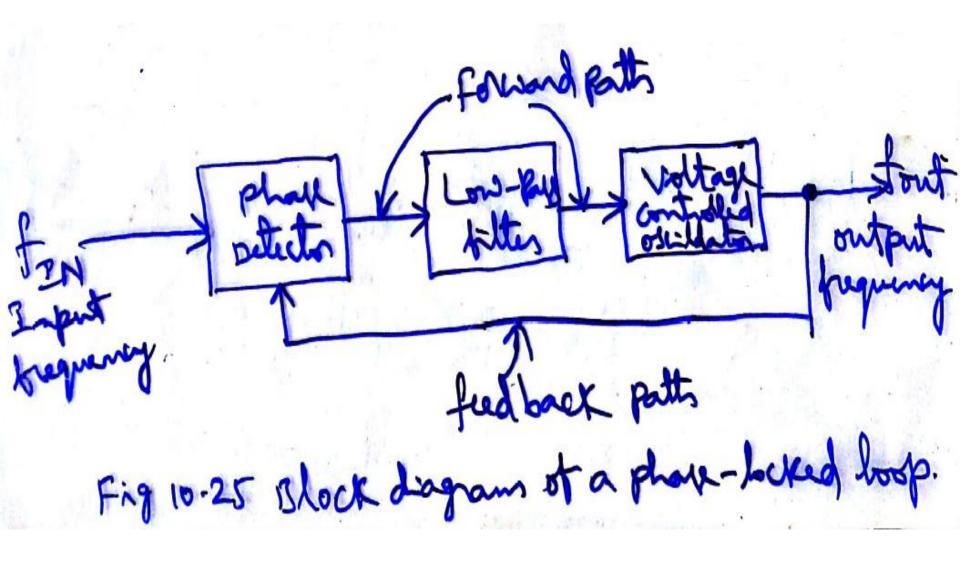

Figure 10.25 shows the phase-Locked loop (PLL) in its basic form.

- As illustrated in this figure, the phase-locked loop consists of (1) a phase detector (2) a low-pass filter (3) a voltage controlled oscillator.

- The phase detector or comparator compares the input frequency fIN with the feed-back frequency fOUT. The output of the phase detector is proportional to the phase difference between fIN and fOUT. The output voltage of a phase detector is a DC voltage and therefore is often referred to as the error voltage.

- The output of the phase detector is then applied to the low pass filter, which removes the high frequency noise and produces a DC level. This DC level, in turn, is the input to the voltage controlled oscillator(VCO).

- The output frequency of the VCO is directly proportional to the input DC level. The VCO frequency is compared with the input frequencies and adjusted until it is equal to the input frequencies.

- In short, the phase locked loop goes through three states: free-running, capture and phase lock.

- Before the input is applied, the phase locked loop is in the free-running state.

- Once the input frequency is applied, the VCO frequency starts to change and the phase locked loop is said to be in the capture mode.

- The VCO frequency continues to change until it equals the input frequency, and the phase-locked loop is then in the phase locked state. When phase locked, the loop tracks any change in the input frequency through its repetitive action.

#### Phase Detector

- The phase detector compares the input frequency and the VCO frequency and generates a DC voltage that is proportional to the phase difference between the two frequencies.

- Depending on the analog or digital phase detector used, the PLL is either called an analog or digital type respectively.

- A double balanced mixer is a classic example of an analog phase detector. On the other hand examples of digital phase detectors are these:

#### Phase Detector cntd...

- 1 Exclusive OR phase detector

- 2 Edge triggered phase detector

- 3 Monolithic phase detector

#### **Exclusive OR Phase Detector:**

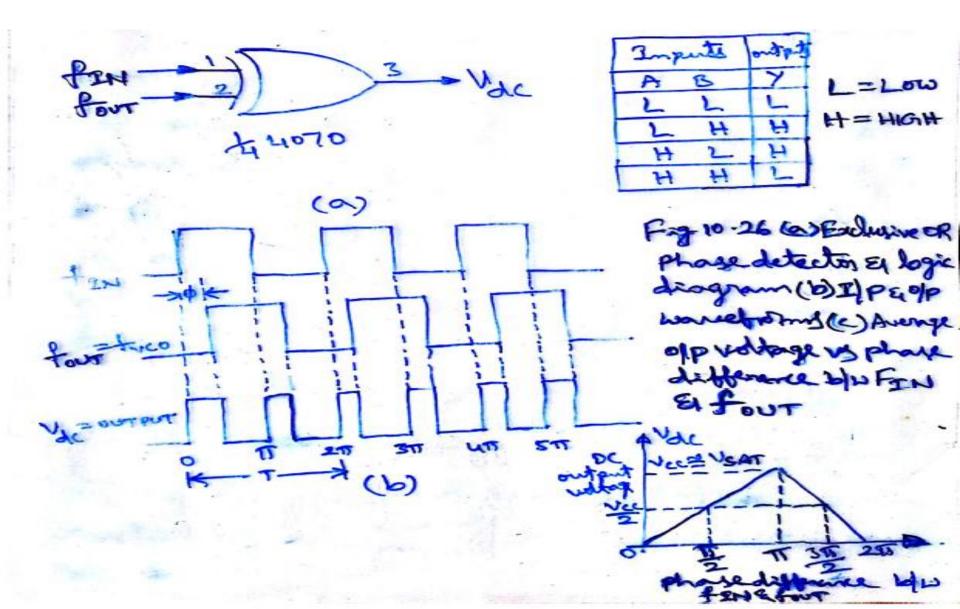

Figure 10.26a shows the exclusive OR phase detector that uses an exclusive OR gate such as CMOS type 4070.

### Phase Detector cntd..

#### Phase Detector cntd...

- The output of the exclusive OR gate is high only when fIN or fOUT is high, as shown in figure 10.26b.

- In this figure, fIN is leading fOUT by φ degrees ie the phase difference between fIN and fOUT is φ degrees.

- The DC output voltage of the exclusive OR phase detector is a function of the phase difference between its two inputs.

#### Phase Detector cntd..

- Figure 10.26 c shows DC output voltage as a function of the phase difference between fIN and fOUT. This graph indicates that the maximum DC output voltage occurs when the phase difference is □ radians or 180 degrees.

- The slope of the curve between 0 and □ radians is the conversion gain Kp of the phase detector.

For example, if the exclusive OR gate uses a supply voltage Vcc = 5 V, the conversion gain Kp is

$Kp = 5V/\Pi = 1.59 V/Radians$

### Phase Detector cntd...

- The exclusive OR type of phase detector is generally used if fIN and fOUT are square waves.

- The edge triggered phase detector, on the other hand, is preferred if the fIN and fOUT are pulse waveforms with less than 50% duty cycles.

- These both types of phase detectors are sensitive to harmonics of the input signal and changes in duty cycles of fIN and fOUT. In such cases Monolithic phase detector is used

#### Low Pass Filter

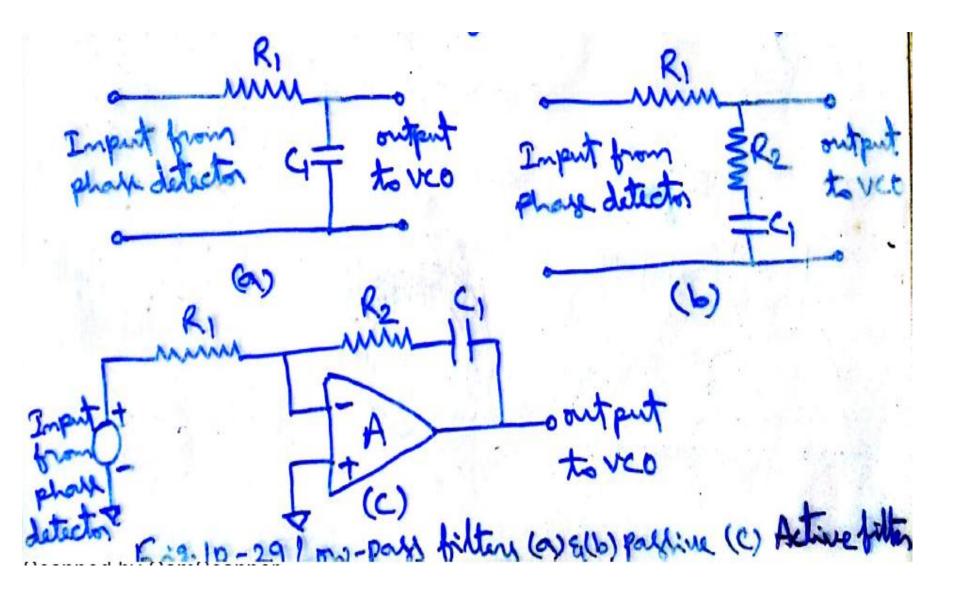

- The second block shown in the PLL block diagram of figure 10.25 is a low-pass filter.

- The function of the low-pass filter is to remove the high frequency components in the output of the phase detector and to remove high frequency noise.

- More important, the low-pass filter controls the dynamic characteristics of the phase-locked loop.

These characteristics include capture and lock ranges, band width, and transient response.

### Low Pass Filter cntd..

- The lock range is defined as the range of frequencies over which the PLL system follows the changes in the input frequency flN. An equivalent term for lock range is the tracking range.

- On the other hand, the capture range is the frequency range in which the PLL acquires phase lock. Obviously the capture range is always smaller than the lock range.

### Low Pass Filter cntd..

- As the filter bandwidth is reduced, it's response time increases. However, reduced band width reduces the capture range of PLL.

- Nevertheless, reduced bandwidth helps to keep the loop in lock through momentary losses of signal and also minimizes the noise

- The loop filter used in the PLL may be one of the three types shown in figure 10.29.

### Low Pass Filter cntd..

### Low Pass Filter cntd...

With the passive filters of Figure 10.29a and b, an amplifier is generally used for gain. On the other hand, the active filter of Figure 10.29c includes the gain.

### Voltage Controlled Oscillator

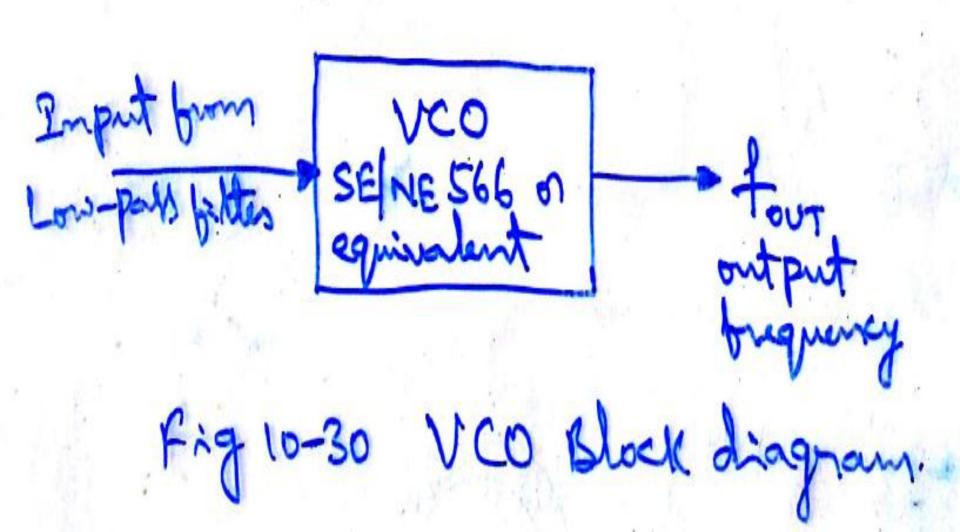

- A third section of the PLL is the voltage controlled oscillator.

- The VCO generates an output frequency that is directly proportional to it's input voltage.

The block diagram of the VCO is shown in Figure 10.30.

### Voltage Controlled Oscillator cntd..

#### 565 PLL

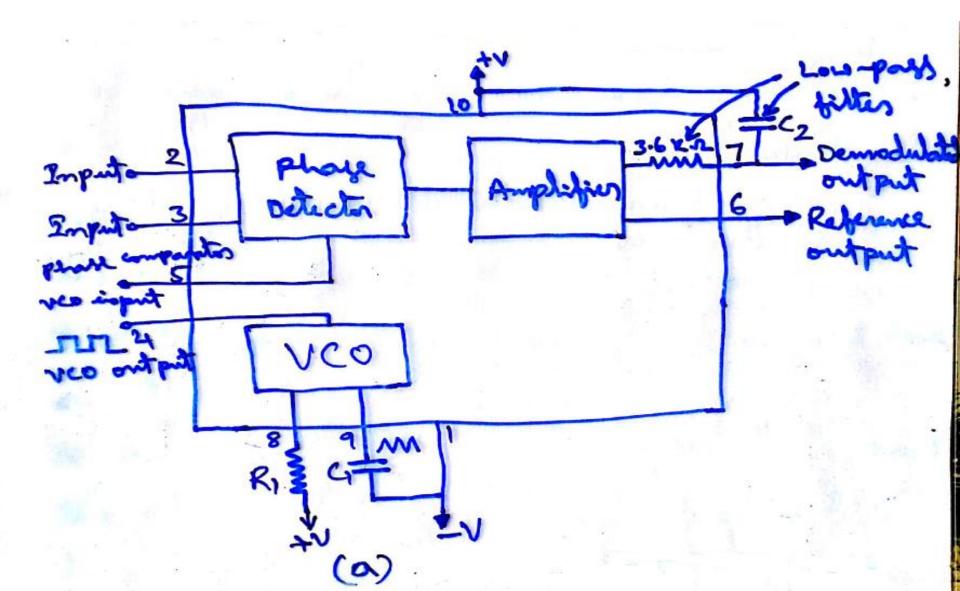

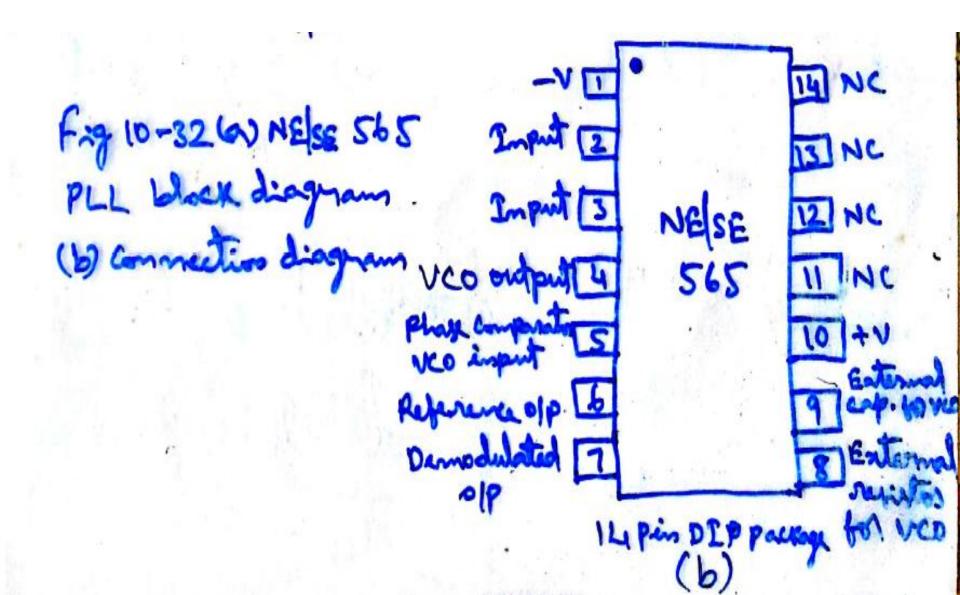

Figure 10.32 shows the block diagram and connection diagram of the 565 PLL. The device is available as a 14 pin DIP package and as 10 pin metal can package.

The central frequency of the PLL is determined by the free running frequency of the VCO, which is given by the equation

fOUT = 1.2/(4 R1 C1) Hz

where R1 and C1 are external resistor and capacitor connected to pins 8 & 9 respectively.

- The VCO free running frequency fOUT is adjusted externally with R1 and C1 to be at the center of the input frequency range.

- Although C1 can be any value, R1 must have a value between 2  $K\Omega$  and 20  $K\Omega$

- A capacitor C2 connected between pin 7 and positive supply (pin 10) forms a first order low-pass filter with an internal resistance of 3.6 K $\Omega$ .

- The filter capacitor C2 should be large enough to eliminate variations in the demodulated output voltage at Pin 7 in order to stabilize the VCO frequency.

- The 565 PLL can lock to and track an input signal over typically + or – 60% bandwidth with respect to fOUT as the center frequency.

- The lock range fL and capture range fC of the PLL are given by the following equations:

fL = + or - 8 fOUT/ V Hz Where fOUT=free running frequency of VCO (Hz) V = v - (-v) volts and fC = + or  $- [fL/((2\pi) (3.6 * 10^3) C2)]^{(1/2)}$  Where C2 is in Farads.

The lock range usually increases with an increase in input voltage but decreases with an increase in supply voltages.

- Pins 2 & 3 are the input terminals and an input signal can be direct-coupled, provided that there is no DC voltage difference between the pins and DC resistances seen from pins 2 & 3 are equal.

- A short between pins 4 & 5 connects the VCO output (fOUT) to the phase comparator and enables the comparator to compare fOUT with the input signal fIN.

### **Applications of PLL**

#### **Frequency Multiplication:**

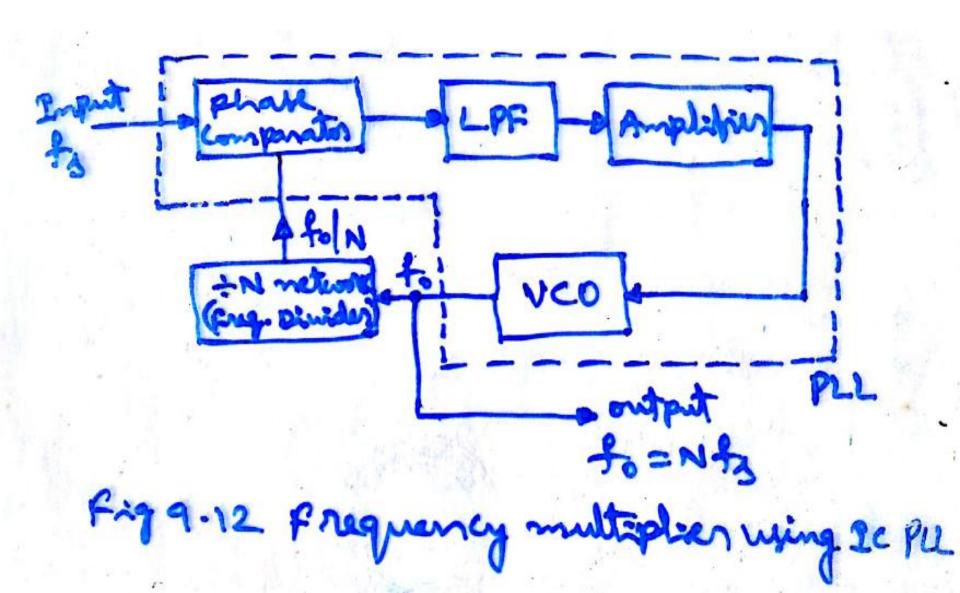

Figure 9.12 gives the block diagram of a frequency multiplier using PLL.

# Frequency Multiplication

### Frequency Multiplication cntd..

- A divide by N network is inserted between the VCO output and the phase comparator input.

- In the locked state, the VCO output frequency fo is given by

fo = Nfs

The multiplication factor can be obtained by selecting a proper scaling factor N of the counter.

End of Unit II

# Unit III

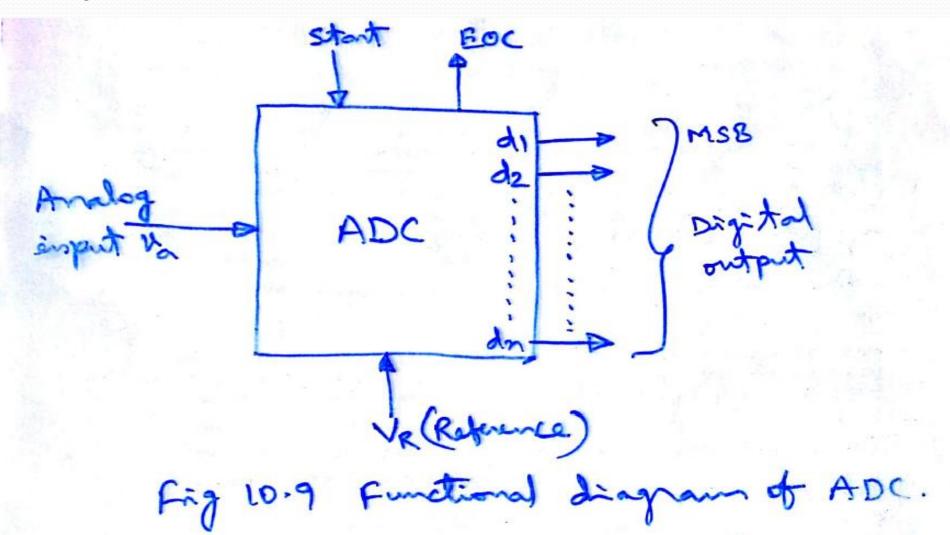

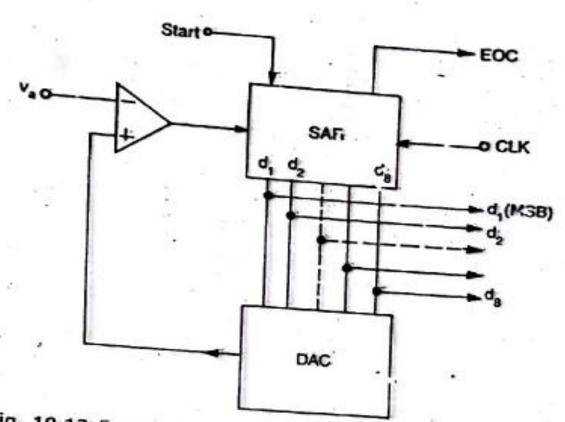

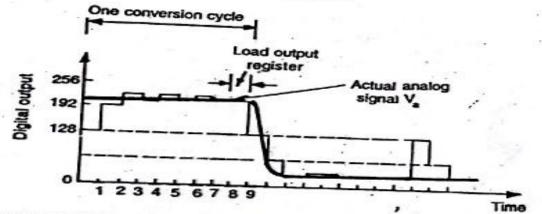

**Data Converters**

### Introduction

- Most of the real world physical quantities such as voltage, current, temperature, pressure and time etc are available in analog form.

- Even though an analog signal represents a real physical parameter with accuracy, it is difficult to process, store, or transmit the analog signal with out introducing considerable error because of superimposition of noise as in the case of amplitude modulation.

- Therefore, for processing, transmission and storage purposes, it is often convenient to express these variables in digital form. It gives better accuracy and reduces noise.

### Introduction cntd...

- The operation of any digital communication system is based upon Analog to Digital (A/D) and Digital to Analog (D/A) convertion.

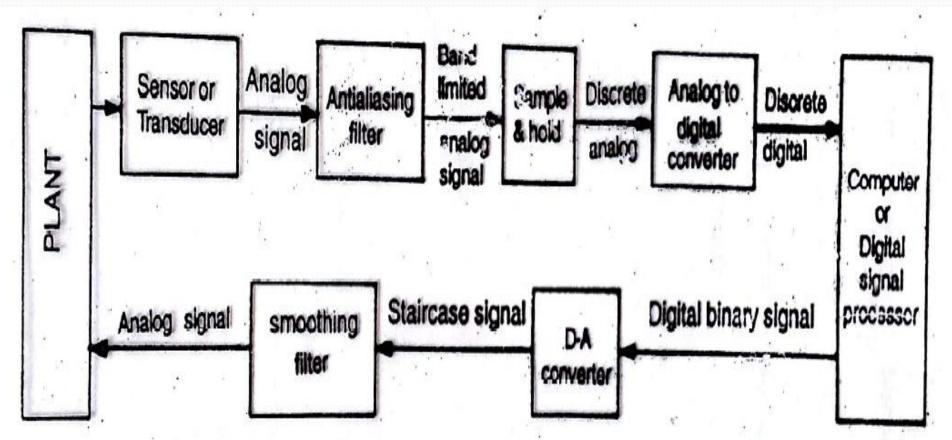

- Figure 10.1, highlights a typical application with in which A/D and D/A conversion is used.

### Introduction cntd..

Fig. 10.1 Circuit showing application of A/D and D/A converter

### Introduction cntd...

- The analog signal obtained from the transducer is band limited by antialiasing filter. The signal is then sampled at a frequency rate more than twice the maximum frequency of the band limited signal.

- The sampled signal has to be held constant while conversion is taking place in A/D converter. This requires that ADC should be preceded by a sample and hold (S/H) circuit.

- The ADC output is a sequence in binary digit. The microcomputer or Digital signal processor performs the numerical calculations of the desired control algorithm.

### Introduction cntd...

- The D/A converter is to convert digital signal into analog and hence the function of DAC is exactly opposite to that of ADC. The D/A converter is usually operated at the same frequency as the ADC.

- The output of a D/A converter is commonly a staircase.

This staircase like output is passed through a smoothing filter to reduce the effect of quantization noise.

### Applications of A/D and D/A conversion

• The scheme given in Figure 10.1 is used either in full or in part in applications such as digital audio recording and playback, computer, music and video synthesis, pulse code modulation transmission, data acquisition, digital multi meter, direct digital control, digital signal processing, microprocessor based instrumentation.

# Basic DAC techniques

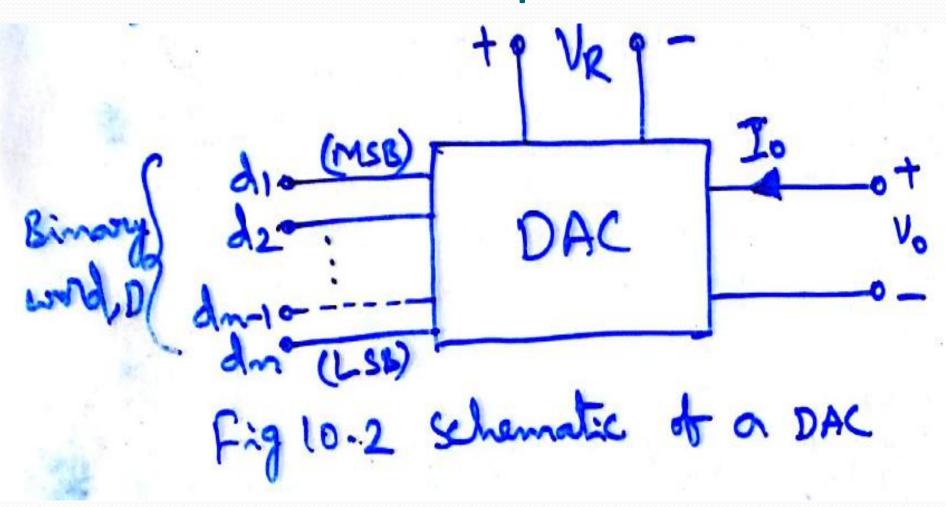

• The schematic of a DAC is shown in Figure 10.2.

# Basic DAC techniques cntd..

# Basic DAC techniques cntd..

- The input is an n-bit binary word D and is combined with a reference voltage vR to give an analog output signal.

- The output of a DAC can be either a voltage or current.

- For a voltage output DAC, the D/A converter is mathematically described as

```

Vo=K Vfs(d1 2^-1 + d2 2^-2 + d3 2^-3+ ---- +dn 2^-n)----(1)

Where Vo = output voltage, Vfs=full scale output voltage

K = scaling factor usually adjusted to unity

d1 d2 d3 ----- dn = n-bit binary fractional word

d1 = MSB with weight of Vfs/2,

dn =LSB with a weight of Vfs/2^n

```

# Basic DAC techniques cntd...

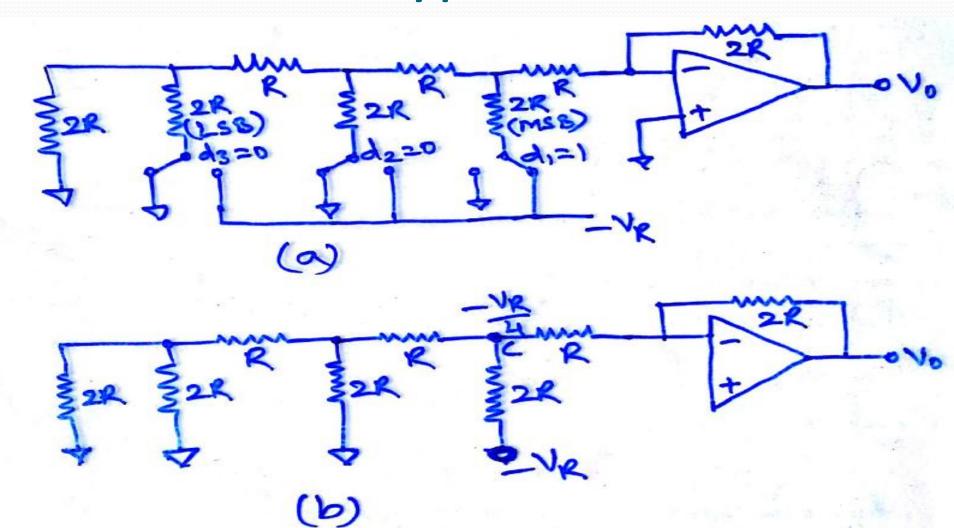

- There are various ways to implement eq(1). Here we shall discuss the following resistive techniques only

- Weighted resistor DAC

- R-2R Ladder DAC

- Inverted R-2R Ladder DAC

#### **Weighted Resistor DAC:**

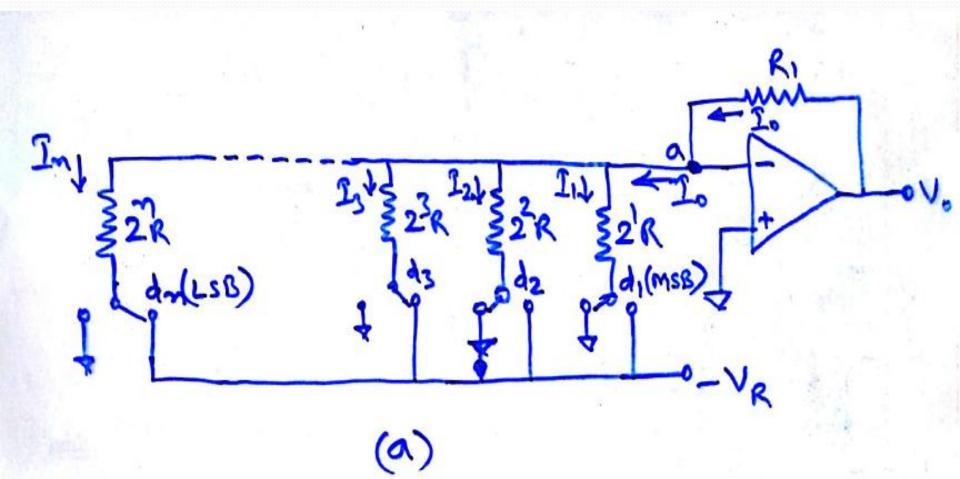

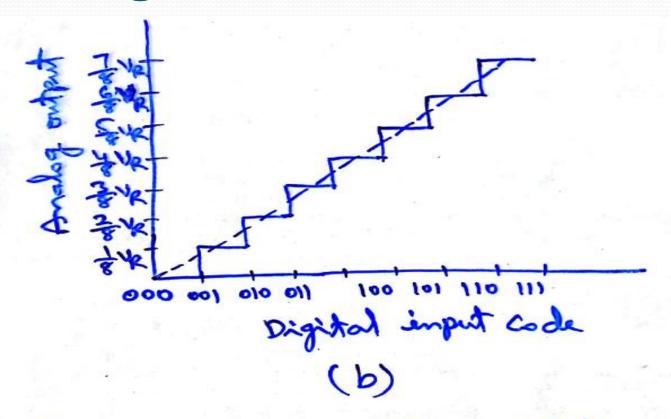

• One of the simplest circuits shown in Figure 10.3a uses a summing amplifier with a binary weighted resistor network. It has n-electronic switches d1, d2, d3, ---- dn, controlled by Binary input word.

# Weighted Resistor DAC cntd..

# Weighted Resistor DAC cntd..

Fig 10.3 (a) A simple weighted resister DAC

(b) Transfer characteristics of a 3-bit

DAC

### Weighted Resistor DAC cntd...

- These switches are single pole double throw (SPDT) type.

- If the Binary input to a particular switch is 1, it connects the resistance to the reference voltage (-Vr). And if the input bit is zero, the switch connects the resistor to ground.

- From Figure 10.3a, the output current Io for an ideal opamp can be written as

```

\begin{split} Io &= I_1 + I_2 + ----- + I_n \\ &= (Vr/(2R)) d_1 + (Vr/(2^2 R)) d_2 + ---- + (Vr/(2^n R)) d_n \\ &= Vr/R (d_1 2^-1 + d_2 2^-2 + ---- + d_n 2^-n) \end{split}

```

The output voltage

Vo=Io Rf=Vr Rf/R

$$(d_1 2^{-1} + d_2 2^{-2} + ---- + d_1 2^{-n}) - (2)$$

## Weighted Resistor DAC cntd...

- Comparing eq(1) with eq(2), we get if Rf = R, then K=1, and Vfs = Vr

- The circuit shown in Figure 10.3a uses a –ve reference voltage. The analog output voltage is therefore +ve staircase as shown in Figure 10.3b for a 3-bit weighted resistor DAC.

- It may be noted that

- Although the op-amp in Figure 10.3a is connected in inverting mode, it can also be connected in non-inverting mode.

### Weighted Resistor DAC cntd...

- The op-amp is simply working as a current-to-voltage converter.

- The polarity of the reference voltage is chosen in accordance with the type of the switch used. For example, for TTL compatible switches, the reference voltage should be +5V and the output will be -ve.

#### Problems with Weighted Resistor DAC

- The accuracy and stability of a DAC depends up on the accuracy of the resistors and tracking of each other with temperature.

- There are, however, a number of problems associated with this type of DAC.

- One of the disadvantages of Binary weighted resistor type DAC is the wide range of resistor values required.

- It may be observed that for better resolution, the input binary word length has to be increased. Thus, as the number of bits increases, the range of resistance value increases.

#### Problems with Weighted Resistor DAC cntd..

- For 8-bit DAC, the resistors required are 2<sup>1</sup> R, 2<sup>2</sup> R, ----, 2<sup>8</sup> R. The largest resistor is 128 times the smallest one for only 8-bit DAC.

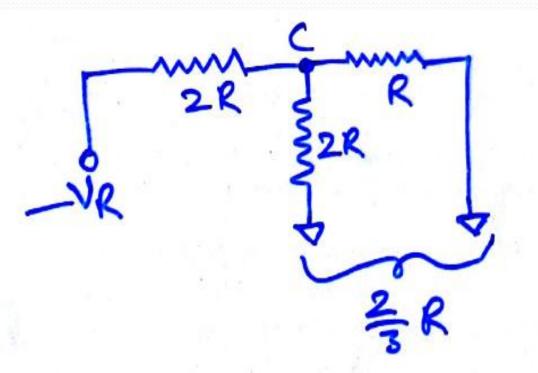

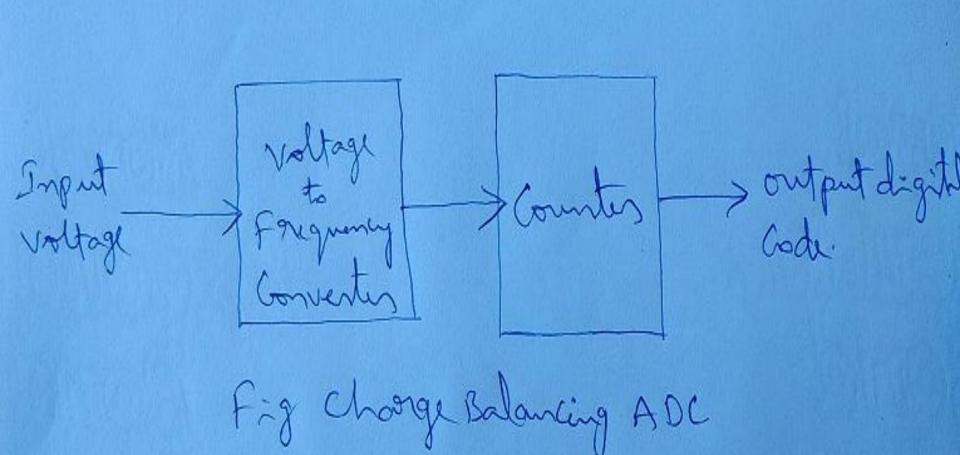

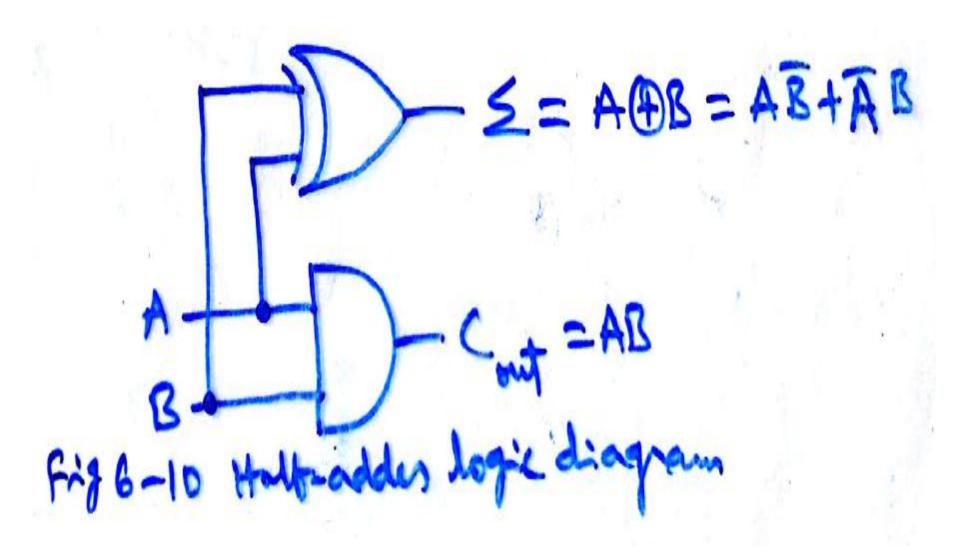

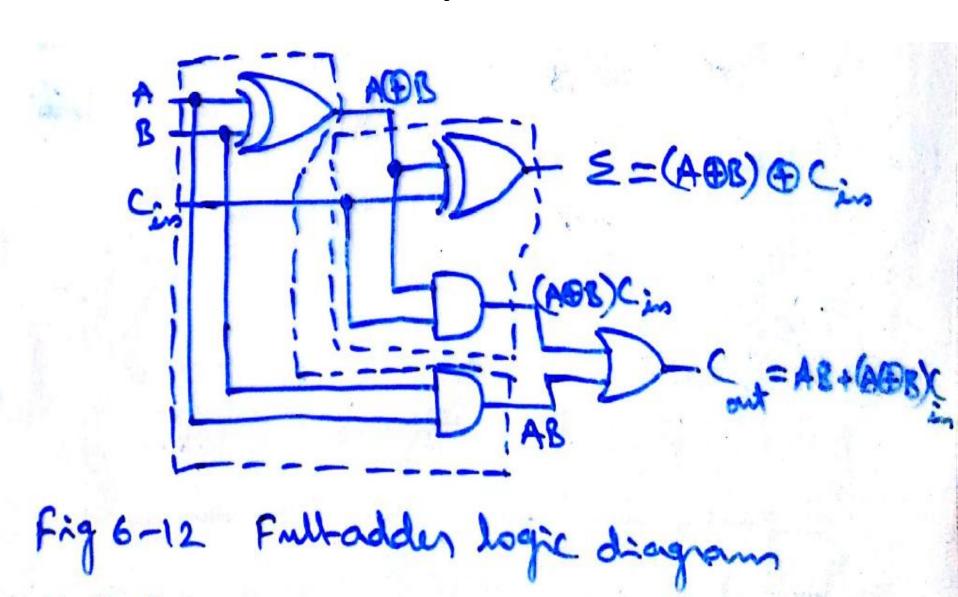

- For a 12-bit DAC, the largest resistance required is 5.12 M $\Omega$  if the smallest is 2.5K $\Omega$ .